Talk:TRIAC/Archive 1

| This is an archive of past discussions about TRIAC. Do not edit the contents of this page. If you wish to start a new discussion or revive an old one, please do so on the current talk page. |

| Archive 1 |

Snubbing

Snubber -- needs an example of snubber used with triac. Not everyone knows what a snubber is and many who do know don't know how it would be used with a triac.Herman 20:31, 23 July 2007 (UTC)

inquries

How to check a triac using multimeter with out current. —The preceding unsigned comment was added by 219.92.48.36 (talk • contribs) .

- With the exception of checking for shorts, I don't think you can check a TRIAC using just an ohmmeter. I'm pretty sure the ohmmeter should see all three terminals as open circuits to the other terminals for both polarities.

- But it would be pretty easy to use a battery-operated test light and a small resistor to trigger the gate.

- Otherwise, unless you have a curve tracer, then observing the TRIAC in the actual circuit using an oscilloscope would be the best test.

Photo

I think I have a spare TRIAC in a parts bin in the theatre I work for, but I am not sure. I will take a photo of it and post it here and if it is a TRIAC then it could be used in the article. -JWGreen 21:40, 25 September 2006 (UTC)

- TRIACs come in all sorts of packages, so this would hardly be representative, especially if it is without adequate identification! DFH 13:44, 26 September 2006 (UTC)

I havea small batch of T2302D's in "modified TO-205 package" (tin can). I'll get my camera back soon and can deliver photos if these are wanted. Their markings are quite clear. Brass or tin coloured? :) blades (talk) 17:42, 10 January 2008 (UTC)

opto coupler for triac

to trigger the triac on AC , an ac current is required. can opto couplers be biased to enable this and provide ac isolation at the same time or is it best to use a triac which incorporates the opto isolation? 216.249.8.77 19:02, 30 October 2006 (UTC)

- As mentioned above, some TRIACs are perfectly happy being triggered by a pulse "of the wrong polarity". Others aren't. For those that aren't happy being so-triggered, pulse transformers driven by bridge circuits provide one alternative as does triggering the main TRIAC with a smaller opto-TRIAC. Other possibilities also exist (limited only by the creativity of the circuit designer). Atlant 19:44, 30 October 2006 (UTC)

12v motor control bi directional

Looking for switching for 12vdc motor, must 200amp spikes motor has. rev mot leads to switch direction, currently use automotive type starter solenoids failure rate is high, because of load. 204.61.205.150 20:02, 10 November 2006 (UTC) brian

Then go to octopart (Octopart) you can search for any components or browse. XU-engineer 18:54, 26 July 2007 (UTC)

The band

There is a band I know named Triac I'd like to add a wiki entry for. Newbie here. Whats the first step in doing that? Just to make another entry that points to a starter one sentence description. Simpliciter 22:27, 16 August 2007 (UTC)

- Well, assuming the band is actually notable, write an article titled TRIAC (band) (or capitalized however they capitalize it). Then put a "disambiguation line" at the top of the TRIAC article that leads people to your new article. But please don't be surprised if your article is deleted for lack of notability.

- Atlant 00:43, 18 August 2007 (UTC)yaa u r right.......

Commentary from top of article

An anonymous user left this at the top of the article. I moved it here in case someone wants to do something about it. Merphant (talk) 06:42, 13 July 2008 (UTC)

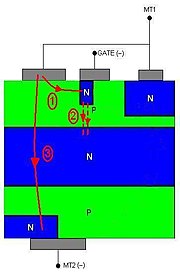

'I suppose the image of constructional view of TRIAC shown in the article is operationally wrong. the uppermost p type semiconductor is conneted directly to gate as well as main terminal 1, which seems to help to trigger the TRIAC by negative as well as positive voltage, but practically it will short circuit the gate signal source. I guess it needs correction'.

- If someone wants to change it it should be like this:

Gate--+

-

|N|

----------------

| | | |

--| P | N | P |-

T1--|N| | | |N|---T2

---------------------

--Dacium (talk) 04:06, 8 August 2008 (UTC)

- As far as I can see from the diagrams in other sources, the gate always touches both N and P material on the MT1 side. The configurations vary, but there's always a connection. It may even be that this is what's changed in the snubberless versions, but I'm not sure ATM. 217.82.118.62 (talk) 16:12, 24 February 2009 (UTC)

scr or triac

which device is more efficient triac or scr —Preceding unsigned comment added by 117.195.98.29 (talk) 07:32, 30 October 2009 (UTC)

that depends on what you want to do and which device you choose, in either case the voltage drop in the on device is comparable, one forward-biased semiconductor junction + resistive losses.210.48.82.11 (talk) 01:57, 2 September 2010 (UTC)

SCR analogy

i'm pretty sure this article is misleading if not downright wrong

If a triac was really equivilent to two thyristors back to back then it wouldn't matter which way round you connected the two main terminals but it DOES matter. The gate voltage must be relative to the correct main terminal or the cuircuit doesn't work Plugwash 21:46, 8 May 2005 (UTC)

- You're right; the SCR analogy isn't precise (but it's close enough that it's often used.)

- Actually, unlike our SCRs, it doesn't matter a huge amount which way you connect the main terminals of a TRIAC. Imagine, if you will, a graph of gate voltage versus (I think) MT2 voltage. With sufficient voltage on the gate, the TRIAC will trigger in *ANY* of those four quadrants. Yes, it triggers more readily in Quadrants I and III (matching polarity on the Gate and MT2), but it will trigger in Quadrants II and IV as well. The real place the "two SCRs" analogy falls down is on turn-off. Two SCRs connected in inverse-parallel will reliably turn off for nearly any load impedance (because each SCR has an entire half-cycle to turn off), but a TRIAC has a very hard time turning off with certain loads; IIRC, inductive loads and the resulting dV/dT will keep the unitary TRIAC device in conduction right through the zero-crossing, requiring use of a snubber to assure turn-off.

well i remember building a simple triac cuircuit and getting the triac the wrong way round stopped it working. if it were the equivilent of two devices in inverse parallell with the gates connected it would make no difference which way round i connected the two MT terminals in the cuircuit Plugwash 01:23, 9 May 2005 (UTC)

- Here's the first article I Googled-up with the query "Quadrant-III triggering":

- The triggering with MT2 positive, as in the figure, is called Quadrant I, while with the supply reversed, it is called Quadrant III. A triac is most sensitive in these two quadrants, but will also respond to gate currents in the other directions. Many modern triacs seem to be symmetrical with respect to MT1 and MT2. To study triggering in Quadrants II and IV, simply interchange the connections of MT1 and MT2.

- There were plenty more.

- You probably got caught by an older TRIAC that wasn't very symmetrical and your trigger simply wasn't providing enough "oomph" to do the job in the "even" quadrants.

- Depending on the circuit, the potential for triggering the TRIAC is derived from the voltage being switched. Especially circuits using the MOC30XX or equivalent optoisolators do that. In these circuits, if you interchange MT1 and MT2, you essentially put the same potential to the gate as is on MT1. And since the trigger voltage is referenced to MT1, this equals zero voltage, hence no firing.

- The interchangability only holds true if you have an external voltage source, which is becoming increasingly unpopular because of the extra components required. 217.82.127.207 (talk) 13:01, 26 February 2009 (UTC)

- I agree with you. It's better to stop telling TRIACs are "like two SCRs in parallel". This is misleading, but unfortunately one often finds this improper phrase even in some specialistic literature. --Vitaltrust (talk) 22:08, 3 April 2011 (UTC)

merge

I suggest merging Alternistor into TRIAC. My understanding is that they are two different names for the same thing, so they should be merged in one article (WP:MERGE), like mountain lion and puma. Even if there is some difference between them, I suspect that difference is small enough that it could be covered in a short statement in the merged article. --68.0.124.33 (talk) 13:50, 29 July 2008 (UTC)

I agree, as far as I understand Alternistor is a trade name for a particular manufacturer's TRIAC design, I'm curious to know if the semiconductor arrangement of the Alternistor is in any way different than a garden-variety TRIAC... Anyone? Athabaska-Clearwater (talk) 03:12, 24 October 2008 (UTC)

- It is different, IIRC in that the gate touches one part of the structure less than it normally does. That lack of connection is the reason why an Alternistor / Snubberless TRIAC cannot be triggered in Q IV, and also the reason why it doesn't have trouble with inductive loads. Thus there is a difference, but it doesn't make it a new device.

- I therefore support the merger, both because it really does not warrant an own article, and also because I am reluctant to accept trademarks as important, despite the current IP hype.

- It might be best if it got it's own section, called "Improved Commutation" or sth. like that, and the trademarks be mentioned only briefly, if at all.

- I suspect that the Alternistor article was started as a marketing ploy, anyway. 217.230.48.46 (talk) 12:50, 23 February 2009 (UTC)

- Actually, not only STMicroelectronics but also other companies, such as Littlefuse, produce this special kind of TRIACs called "Alternistors". However, I don't think alternistors are worth having their own section: maybe they could be briefly described somewhere in the article under, for example, a "Special TRIACs" section. Moreover, I think that any reference to manufacturers should be erased: Wikipedia isn't the right place for advertising. --Vitaltrust (talk) 17:43, 3 April 2011 (UTC)

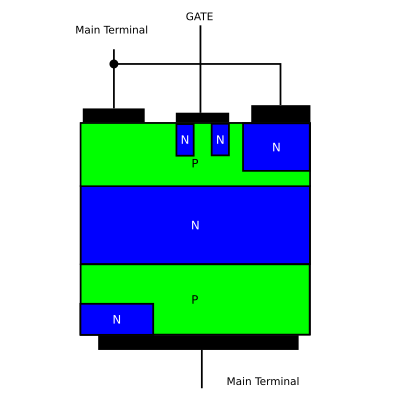

Consider changing figure

I cannot find the reason why on one of the figures of the page, which I report below for convenience, there are two n-type layers under the gate terminal:

I think that this could interfere with the triggering in the fourth quadrant, where holes are needed to inject into the n-layer below the A1/MT1 terminal. Indeed, in many books I find an internal structure which is much closer to the following one, rather than the one in the article:

For example, see [Thyristor Theory and Design Considerations, ON Semiconductor], on page 24.

Before substituting the figure, I will wait a week starting from now, hoping there is consensus. Please consider that, as I wrote, in literature one usually finds an internal structure which has only one p-layer and one n-layer adjoining the gate terminal. --Vitaltrust (talk) 17:46, 18 April 2011 (UTC)

- Having read no opposing words, I'll proceed with the change. --Vitaltrust (talk) 21:06, 24 April 2011 (UTC)

Archiving old topics

I'm going to ask MiszaBot I to automatically archive the conversations older than 180 days of this page. There are topics no one seems to care any longer about, which have been left here for years.

I have put the relevant code to invoke the bot at the beginning of the page:

{{User:MiszaBot/config

| algo = old(180d)

| archive = Talk:TRIAC/Archive %(counter)d

| counter = 1

| maxarchivesize = 100K

| archiveheader = {{talk archive navigation}}

| minthreadstoarchive = 1

| minthreadsleft = 4

}}

If someone does not agree with me, just erase that code and explain why. --Vitaltrust (talk) 19:46, 26 April 2011 (UTC)

suitable capacitors

I was just curious i was reading and saw the part about 100nF capacitors being suitable for use and without thinking i edited it to "mF" but after thinking about it i undid my own edit.I undid it because i was unsure wether it was a spelling error like i initially thought it was an innocent typo, or wether it was referring to millifarads? if someone could clarify for me it would be great! im not trying to split hairs i actually am just curious. — Preceding unsigned comment added by 24.177.53.17 (talk) 02:32, 1 October 2011 (UTC)

- Nanofarads, not millifarads. A millifarad capactor passes a lot of current at power line frequency. --Wtshymanski (talk) 13:56, 1 October 2011 (UTC)

- It's very unusual to find millifarad capacitors in Electronics. Indeed, such value is very high. I cited a reference about the technique to put a capacitor between the gate and A1 (MT1), and actually you find there 100nF. Vitaltrust (talk) 22:39, 19 October 2011 (UTC)

It's not true that a TRIAC equals two SCRs!

I want to delete from the article all the parts which might mislead the reader and make him or her think that two anti-parallelized SCRs are equivalent to a TRIAC. In fact, this is not true and may lead to confusion!

SCRs are unidirectional devices, not only in the way they conduct the main current, but also in triggering: you can trigger an SCR only by injecting a gate current. TRIACs, on the other hand, are bidirectionally-triggered devices and can be triggered even if you drive current out of the gate, as it does happen in the II and III quadrants of operation.

In the next few days, I'm going to start correcting the article. Meanwhile, I will wait for your opinions about this issue. Vitaltrust (talk) 23:14, 19 October 2011 (UTC)

- SUre, take it out. It's so loosely applicable, that we'd be much more concise in just saying "Unlike a unidirectional SCR, a TRIAC conducts in two directions" etc. and mention that antiparallel SCRs would have very assymetric triggering behavior. --Wtshymanski (talk) 15:17, 20 October 2011 (UTC)

I think we can sort it out in this way:

| Present revision | Proposed revision | |

|---|---|---|

| Second paragraph | Silicon-controlled rectifiers (SCRs) are unidirectional (one-way) current devices, making them useful for controlling DC only. If two SCRs are joined in back-to-back parallel fashion just like two Shockley diodes were joined together to form a DIAC, we have a new device known as the TRIAC. | TRIACs belong to the thyristor family and are closely related to SCRs. However, unlike SCRs, which are unidirectional devices (i.e. can conduct current only in one way), TRIACs are bidirectional and so current can flow accross them in either direction. Another difference from SCRs is that a TRIAC can be triggered by either a positive or a negative current being applied to its gate electrode, whereas SCRs can be triggered only by currents going into the gate. In order to create a triggering current, a positive or negative voltage has to be applied to the gate with respect to the A1 terminal (otherwise known as MT1). |

| Third paragraph | A TRIAC is approximately equivalent to two complementary unilateral thyristors (one is anode triggered and another is cathode triggered SCR joined in antiparallel (paralleled but with the polarity reversed) and with their gates connected together. It can be triggered by either a positive or a negative voltage being applied to its gate electrode (with respect to A1, otherwise known as MT1). Once triggered, the device continues to conduct until the current through it drops below a certain threshold value, the holding current, such as at the end of a half-cycle of alternating current (AC) mains power. This makes the TRIAC a very convenient switch for AC circuits, allowing the control of very large power flows with milliampere-scale control currents. In addition, applying a trigger pulse at a controllable point in an AC cycle allows one to control the percentage of current that flows through the TRIAC to the load (phase control). | Once triggered, the device continues to conduct until the current through it drops below a certain threshold value, the holding current, such as at the end of a half-cycle of alternating current (AC) mains power. This makes the TRIAC a very convenient switch for AC circuits, allowing the control of very large power flows with milliampere-scale control currents. In addition, applying a trigger pulse at a controllable point in an AC cycle allows one to control the percentage of current that flows through the TRIAC to the load (phase control). |

I will wait a couple of days for suggestions or improvements, then I will proceed with the substitution. --Vitaltrust (talk) 22:04, 21 October 2011 (UTC)

![]() Done. No one has objected up to now, so I have proceeded with the changes. --Vitaltrust (talk) 13:09, 23 October 2011 (UTC)

Done. No one has objected up to now, so I have proceeded with the changes. --Vitaltrust (talk) 13:09, 23 October 2011 (UTC)

Request for rating upgrade.

I have requested a rating upgrade to the Wikipedia:WikiProject_Electronics. Indeed, I think the present "start class" rating no longer applies to this article, given the extensive improvements we have made in the last few months. --Vitaltrust (talk) 13:34, 23 October 2011 (UTC)

![]() Done. Upgrade achieved. --Vitaltrust (talk) 15:28, 29 October 2011 (UTC)

Done. Upgrade achieved. --Vitaltrust (talk) 15:28, 29 October 2011 (UTC)

Request of explanation: why Q-IV is the least sensitive quadrant?

Can anybody explain why the fourth quadrant requires the most current to trigger the device? As a circuit designer, I always find this both in literature and on the datasheets, but I've never found an explanation of what causes this behaviour at the semiconductor level. --Vitaltrust (talk) 15:48, 29 October 2011 (UTC)

- Yeah, that's what my original {{clarify}} was really about. So, I've restored the {{clarify}} and added others where Q-IV and Q-I sensitivity is addressed. I understood that Q-IV is the least sensitive and the generic definition of "less sensitive" (which is why I edited that from the article) but why Q-IV is the least sensitive (and Q-I is most sensitive) isn't explained in the article.

Okay, here's an attempt to explain it. What's important to remember is that the two cross-connected transistors in a thyristor are not designed for high beta; rather, they are usually optimized for things like standoff voltage. This is mostly carried by the inner N layer, which is very lightly doped (N−); the N layers adjacent to the electrodes are more heavily doped (N+).

For a 4-layer thyristor to operate, the product of the current gains of the two transistors must exceed 1. Note that one of the betas may be and often is less than 1! Only the product matters. The important thing to remember is that these are very low-beta transistors. Just because I talk about a set of 3 layers making a transistor does not mean there's current gain.

First, start with the basic quadrant I and II operation, where the main transistors are NPN on top and PNP below.

In quadrant 1, the gate is shoving current straight into the base of the NPN transistor, making it easy to trigger.

In quadrant 2, the base does not trigger the NPNP transistor stack directly, but rather the it is the emitter of a secondary NPN, with A1 as the base, and the inner N− layer being the collector. When the collector current is high enough, this turns on the PNP of the main thyristor stack and things start to happen. But this first transistor has less than unity current gain, requiring more gate current to fire up the thyristor stack. Despite having less than unity gain, it's a separate transistor, and some work can be put into optimizing its operation.

In quadrant 3, the main stack is no longer NPN on top, but rather PNPN, with the top A1 conducting through its P layer, and the bottom A2 conducting through its N+ layer. Again, these transistors have a combined current gain barely more than 1.

Despite this change, triggering is almost the same as in quadrant 2. The same secondary NPN is used to pull current out of the the N− base of the main PNP, turning on the stack; it's only the location of the main NPN that differs.

Now, quadrant 4. Here's where things get interesting. Like quadrant 1, the gate current goes straight into the base of a "main" NPN. However, this NPN is no longer on the main current path! Because the thyristor is flipped, the active "main" NPN is now on the other side, adjacent to A2. Rather, this transistor, which is designed and optimized to be a "main" transistor, has to be turned on soley by the gate current, with no help from positive feedback, until it pulls enough current out of the main PNP to start the thyristor stack.

You may recall that the beta of a silicon transistor is maximized for a "medium" collector current. At low currents, the beta is lower than normal. And the gate current, spread out across the huge main transistor area, is definitely operating in that region. (Quadrant 1 suffers from the same problem, but the positive feedback quickly starts to kick in and solve it for us.)

So the upshot is that Quadrant 1 triggers the internal SCR directly. Quadrants 2 and 3 do so via an auxiliary NPN, which is a pretty bad NPN, but at least it's small and not too hard to turn on. But quadrant 4 has to turn on a large main NPN to turn on the internal SCR, which takes a lot of current.

Does that make sense? 71.41.210.146 (talk) 06:50, 15 April 2012 (UTC)

- As a follow-up, let me see if I can draw a TRIAC as four transistors using ASCII art.

- First of all, a 5-layer DIAC is basically

A1

|

+--+--+

| /

| n (E)

+---p

| n (C)

\ \

p |

n---+

p |

/ /

| n (C)

+---p

| n (E)

| \

+--+--+

|

A2

- Now, let me add the gate, which is a secondary NPN in parallel with A1's:

A1 G

| |

+--+--+ +-+-+

| / | /

| n | n (E)

+---p---+-p Q2 Q4

| n n (C)

\ \ \

p | |

n---+-----+ Q1

p |

/ /

| n (C)

+---p Q3

| n (E)

| \

+--+--+

|

A2

- In quadrants 1 and 2, the main thyristor is Q1 and Q2. In quadrants 3 and 4, the main thyristor is Q1 and Q3.

- In quadrants 1 and 4, the gate current turns on Q2, by injecting holes directly into its base. In quadrants 2 and 3, the gate current turns on Q4 by pulling its emitter down while A1 provides the base current.

- Either way, the result is base current pulled out of Q1's base, and the thyristor turns on.

- When understanding the gate action, it's important to recognize that there's significant resistance in the P layer, which divide all the transistors into lots of little transistors connected in parallel. Even through the circuit shows A1 and G connected by it, they are not necessarily at the same voltage. Some current flows (the dotted line in Figure 3), but enough flows across Q2's B-E junction to turn it on.

- Likewise, in quadrants 2 and 3, the gate can pull Q4's emitter below the base (held high by A1) to turn it on.

- The hardest thing is quadrant 4 triggering, where the gate has to turn on Q2, but there's no voltage on the collector to help.

- 71.41.210.146 (talk) 16:39, 15 April 2012 (UTC)

- Overall, I largely agree with your explanation. I agree that the main reason is probably that you have to drag current out of the "central" N-layer, even acting against the voltage potential (in quadrant IV MT2 is'-'), using a structure that is farther from the main current path than quadrant III (where actually the triggering process is similar). However, it is better to provide some references before putting all this into the article. Do you have any sources? —Vitaltrust (talk) 21:27, 22 April 2012 (UTC)

Unfortunately, no I don't have sources; I worked it out from first principles. And after thinking hard about what you wrote, I realize that my explanation on Q-IV is incomplete, and there's a far more obvious effect causing the difference.

In Q-I operation, the main current path is A1-NPNP-A2(+). The two NP junctions have one Vbe drop across them (nominally 0.7V, but actually much less when in the off state, as the current is negligible), and the main PN junction bears the brunt of the standoff voltage. This is the collector-base junction of the two transistors. The gate connects to the base of the initial NPN, and when it is pulled high, the transistor is operating in the "active" region, with significant collector-emitter voltage, and thus high beta.

In Q-IV, the main current path is A1-PNPN-A2(−). The two PN junctions have Vbe forward drops across them, and the NP junction is the collector-base junction of the two transistors, and holds the standoff voltage.

The gate connects to the base of a separate NPN, whose emitter is also A1, and whose collector is the base of the PNP. When you put current across this transistor's base-emitter junction (by raising the gate one Vbe above A1), the collector voltage is one diode drop less than A1. (As mentioned before, this is a lot less than 0.7V, in fact almost 0V, because the forward current is almost zero.)

This is deep in the saturation region, where a transistor's effective beta is greatly reduced. The main thyristor is triggered identicially to Q-III, but with the collector current of this transistor rather than the gate current directly. It never was a high-beta transistor to start with, and now it's trying to operate with a slightly *reversed* Vce, reducing it to something less than unity. Thus, the Q-IV triggering current is more than the Q-III triggering current.

Does that make sense? 71.41.210.146 (talk) 23:35, 25 April 2012 (UTC)

- Well, let me put my comments directly into the text you wrote above and put there my remarks.

In Q-I operation, the main current path is A1-NPNP-A2(+).

The two NP junctions have one Vbe drop across them (nominally 0.7V, but actually much less when in the off state, as the current is negligible), and the main PN junction bears the brunt of the standoff voltage. This is the collector-base junction of the two transistors.

The two NP junctions have one Vbe drop across them (nominally 0.7V, but actually much less when in the off state, as the current is negligible), and the main PN junction bears the brunt of the standoff voltage. This is the collector-base junction of the two transistors. I agree. Since both the NPN (adjoining MT1 and GATE) and the PNP (adjoining MT2) must be off, the base of the PNP must be higher than VMT2-0.7V, much of the voltage across the whole device is borne by the junction between the collector and the base of the NPN, which is at the same time the junction between the base and the collector of the PNP. The gate connects to the base of the initial NPN, and when it is pulled high, the transistor is operating in the "active" region, with significant collector-emitter voltage, and thus high beta.

I agree. Since both the NPN (adjoining MT1 and GATE) and the PNP (adjoining MT2) must be off, the base of the PNP must be higher than VMT2-0.7V, much of the voltage across the whole device is borne by the junction between the collector and the base of the NPN, which is at the same time the junction between the base and the collector of the PNP. The gate connects to the base of the initial NPN, and when it is pulled high, the transistor is operating in the "active" region, with significant collector-emitter voltage, and thus high beta.  Ok, but I think that what you say about the active region is right only during the turn-on process, when the voltage across the two latching transistor is equal to the off-state voltage. After the turn-on process has ended, I think that neither transistor can be in active the region, or at most only one of the two (the other being in saturation): if both were in the forward active region, the would have β≫1, but since the collector of Q1 is the base of Q2, you would have ; but the collector of Q2 (NPN) is also the base of Q1 (PNP) and therefore , which means that , but this is not consistent with our starting hypothesis that both transistors were in the active region. Thus, at least one of the two transistors must be in saturation, and since the VCE of a saturated BJT is typically no more than 0.3V (the VBE(sat), on the other hand, is typically over 0.8V), from a designer's point of view it is better to have both the transistors in saturation in order to get a lower voltage drop between MT1 and MT2, so they maybe try to design both transistors in such a way, I think.

Ok, but I think that what you say about the active region is right only during the turn-on process, when the voltage across the two latching transistor is equal to the off-state voltage. After the turn-on process has ended, I think that neither transistor can be in active the region, or at most only one of the two (the other being in saturation): if both were in the forward active region, the would have β≫1, but since the collector of Q1 is the base of Q2, you would have ; but the collector of Q2 (NPN) is also the base of Q1 (PNP) and therefore , which means that , but this is not consistent with our starting hypothesis that both transistors were in the active region. Thus, at least one of the two transistors must be in saturation, and since the VCE of a saturated BJT is typically no more than 0.3V (the VBE(sat), on the other hand, is typically over 0.8V), from a designer's point of view it is better to have both the transistors in saturation in order to get a lower voltage drop between MT1 and MT2, so they maybe try to design both transistors in such a way, I think. In Q-IV, the main current path is A1-PNPN-A2(−). The two PN junctions have Vbe forward drops across them, and the NP junction is the collector-base junction of the two transistors, and holds the standoff voltage.

The gate connects to the base of a separate NPN, whose emitter is also A1, and whose collector is the base of the PNP.

WhenImmediately after you put current across this transistor's base-emitter junction (by raising the gate one Vbe above A1), i.e. at the start of the turn-on process, the collector voltage is one diode drop less than A1. I agree, but only if you put into the text the two slight clarifications I have made.

I agree, but only if you put into the text the two slight clarifications I have made. (As mentioned before, this is a lot less than 0.7V, in fact almost 0V, because the forward current is almost zero.) During the turn-on process, the "collector" of the NPN transistor is at near-zero potential because the transistor is saturated, not because current is low. In fact, remember that Q-IV needs the largest gate current among the four quadrants to turn on, and it can be in the order of tens of milliamps. Moreover, it is important to notice that in Q-III and Q-IV the voltage during the off-state drops accross the junction between the "central" n-layer and the lower p-layer of figure 6:

During the turn-on process, the "collector" of the NPN transistor is at near-zero potential because the transistor is saturated, not because current is low. In fact, remember that Q-IV needs the largest gate current among the four quadrants to turn on, and it can be in the order of tens of milliamps. Moreover, it is important to notice that in Q-III and Q-IV the voltage during the off-state drops accross the junction between the "central" n-layer and the lower p-layer of figure 6:This is deep in the saturation region,

Yeah! where a transistor's effective beta is greatly reduced.

Yeah! where a transistor's effective beta is greatly reduced. Does it make sense to talk about β in the saturation mode?

Does it make sense to talk about β in the saturation mode? The main thyristor is triggered identicially to Q-III, but with the collector current of this transistor rather than the gate current directly. It never was a high-beta transistor to start with, and now it's trying to operate with a slightly "reversed" Vce, reducing it to something less than unity. Thus, the Q-IV triggering current is more than the Q-III triggering current. Actually, the only difference I can notice between the two triggering modes (Q-III and Q-IV) is their different distance from the final current path. Please compare the description of Q-III and Q-IV in the main article.

Actually, the only difference I can notice between the two triggering modes (Q-III and Q-IV) is their different distance from the final current path. Please compare the description of Q-III and Q-IV in the main article.- So, just to summarize, I think that the key points of the issue are the following facts:

- the triggering process in Q-IV starts with a transistor which is in saturation from the beginning of its operation, so you have to drive more current into the gate to have it turned on because you cannot use the transistor's current amplification capability;

- in Q-IV, the turn-on process begins farther from the final PNPN main conducting structure than in Q-III: this is not something secondary in importance, because at the beginning of the turn on process you have to lower the voltage of the large central n-layer by diffusing into it electrons from the MT1 terminal through a saturated transistor. Those electrons are diffusing against the voltage potential, which tends to attract them back into the upper p-layer (see the figure I put above), so if you want them to reach that region of the central n-layer where the final conduction takes place you have to offset the electrons which escape back by driving more gate current than in Q-III.

- This is my opinion about why Q-IV is the most unfavorable of the four triggering modes. I unfortunately haven't found references to confirm it yet and it seems quite hard to find an explanation to this issue in literature. —Vitaltrust (talk) 19:39, 29 April 2012 (UTC)

First of all, thank you for a very interesting and enlightening discussion! I'm about to disagree with you, but I don't want to appear irritated or short-tempered. Like you, I haven't found a good reference explaining this and I'm having fun working it out. The following is what I think is happening, but I won't be sure until iy makes sense to someone else as well.

Ok, but I think that what you say about the active region is right only during the turn-on process, when the voltage accross the two latching transistor is equal to the off-state voltage ![]() Yes; I had intended that to be obvious. I am only taking about the initial triggering of the TRIAC; once the current through the main terminals is sufficient to collapse the voltage across the TRIAC, the gate is no longer relevant.

Yes; I had intended that to be obvious. I am only taking about the initial triggering of the TRIAC; once the current through the main terminals is sufficient to collapse the voltage across the TRIAC, the gate is no longer relevant.

After the turn-on process has ended, I think that neither transistor can be in active the region, or at most only one of the two (the other being in saturation) ![]() I think you'll find that both transistors are on the edge of saturation, but technically in the active region. The definition of the boundary is when the collector-base voltage is zero (Vbe = Vce), and whatever happens inside the thyristor, there has to be a monotone voltage gradient across the PNPN stack. So the PNP's collector is a lower voltage than its base, and similarly the NPN's collector is at a higher voltage than its base.. Now, what happens is that the collector voltage drops until the beta drops to the point that the product of the current gains equals 1, so it's not in the normal "high beta" active region. Your math is absolutely right, and thinking in terms of saturation is better, but technically both are active. (To quote Bipolar junction transistor#Regions of operation: "Although these regions are well defined for sufficiently large applied voltage, they overlap somewhat for small (less than a few hundred millivolts) biases.")

I think you'll find that both transistors are on the edge of saturation, but technically in the active region. The definition of the boundary is when the collector-base voltage is zero (Vbe = Vce), and whatever happens inside the thyristor, there has to be a monotone voltage gradient across the PNPN stack. So the PNP's collector is a lower voltage than its base, and similarly the NPN's collector is at a higher voltage than its base.. Now, what happens is that the collector voltage drops until the beta drops to the point that the product of the current gains equals 1, so it's not in the normal "high beta" active region. Your math is absolutely right, and thinking in terms of saturation is better, but technically both are active. (To quote Bipolar junction transistor#Regions of operation: "Although these regions are well defined for sufficiently large applied voltage, they overlap somewhat for small (less than a few hundred millivolts) biases.")

During the turn-on process, the "collector" of the NPN transistor is at near-zero potential because the transistor is saturated, not because current is low. ![]() While we can argue about the direction of the cause and effect arrow (are raindrops falling because it is raining, or is it raining because raindrops are falling?), the potential is zero before turn-on starts, because the current is low. Turning on (adding gate current) doesn't change that, but does change the base voltage, which then establishes the conditions for saturation (base voltage higher than collector voltage). Because the collector voltage was low before the saturation condition was established, I have a hard time saying that the former happened because of the latter.

While we can argue about the direction of the cause and effect arrow (are raindrops falling because it is raining, or is it raining because raindrops are falling?), the potential is zero before turn-on starts, because the current is low. Turning on (adding gate current) doesn't change that, but does change the base voltage, which then establishes the conditions for saturation (base voltage higher than collector voltage). Because the collector voltage was low before the saturation condition was established, I have a hard time saying that the former happened because of the latter.

Does it make sense to talk about β in the saturation mode? Absolutely! It's simply the ratio of collector current to base current, so it's defined whenever base current is non-zero.

Actually, the only difference I can notice between the two triggering modes (Q-III and Q-IV) is their different distance from the final current path. Please compare the description of Q-III and Q-IV in the main article. ![]() Whoa! I certainly agree that there are strong similarities due to the same final current path, but there's a huge difference! It's the same in that an NPN separate from the final current path injects current into the base of the "main" PNP, but note the differences:

Whoa! I certainly agree that there are strong similarities due to the same final current path, but there's a huge difference! It's the same in that an NPN separate from the final current path injects current into the base of the "main" PNP, but note the differences:

- In Q-III, the gate is the emitter of an NPN, which is in saturation when triggered, but only slightly. Vce and Vbe are both positive, and almost the same (although Vbe is higher, since the collector is one low-current diode drop lower than the base).

- In Q-IV, the gate is the base, and Vce is not only zero, it's actually slightly negative. This is nowhere near the edge of saturation.

Now I'm curious what you'll find laughably wrong about what I've written! ![]() 71.41.210.146 (talk) 07:11, 1 May 2012 (UTC)

71.41.210.146 (talk) 07:11, 1 May 2012 (UTC)

- Hi! Well, first of all, I would like to thank you too for this interesting discussion. I don't know if our talk is going towards the right direction, since we haven't found any sources to confirm either opinion so far, unfortunately. But nevertheless it is a good brain-training and for me also an occasion to take a look again to some concepts I studied when I was at the university, some years ago...

- First of all, regarding this paragraph:

During the turn-on process, the "collector" of the NPN transistor is at near-zero potential because the transistor is saturated, not because current is low.

While we can argue about the direction of the cause and effect arrow (are raindrops falling because it is raining, or is it raining because raindrops are falling?), the potential is zero before turn-on starts, because the current is low. Turning on (adding gate current) doesn't change that, but does change the base voltage, which then establishes the conditions for saturation (base voltage higher than collector voltage). Because the collector voltage was low before the saturation condition was established, I have a hard time saying that the former happened because of the latter.

While we can argue about the direction of the cause and effect arrow (are raindrops falling because it is raining, or is it raining because raindrops are falling?), the potential is zero before turn-on starts, because the current is low. Turning on (adding gate current) doesn't change that, but does change the base voltage, which then establishes the conditions for saturation (base voltage higher than collector voltage). Because the collector voltage was low before the saturation condition was established, I have a hard time saying that the former happened because of the latter.

- Ok, written in these words, I agree. Maybe there was some misunderstanding between us on this point.

- Saturation

- Regarding your statement about the operation mode of the two latching resistors, as I told you, if Math isn't an opinion they must have , so they cannot be both in the forward active region (unless they have both β=1 by design, which seems quite odd). Obviously, this seems to imply that the voltage accross the device is not monotone, but has it necessarily to be? We have two latching transistor, not a resistor, so I don't see a non-monotone voltage pattern as something impossible. I remember I designed a net with two transistor in a similar fashion some time ago and the design assumption was that both of them had to be in saturation: once triggered, the base of the pnp is kept at a low voltage by the current dragged by the collector of the npn and, vicecersa, the base of the npn is kept high by the collector of the pnp. So I don't agree on this matter, but on the other hand I think it is something not very important: I hope none of us doubts that the two transistors keep each other turned on.

- Beta

- Beware that, strictly speaking, β isn't simply , but instead it is a specific constant of a particular transistor, so it is not so straightforward to talk about β in the saturation mode. If we go into the physics of the device, you get this interesting formula as a direct consequence of the Ebers-Moll model for a npn transistor:

- In this formula, ICEO is the current flowing from the collector to the emitter with the base shorted to the emitter and a reverse-biased base-to-emitter junction (VBC < 0), so it is very low; VT is the so-called "thermal voltage", which is about 25-26mV at 30°C. You can find a proof here, but the document is in Italian. As soon as I find something similar in English, I will update the link.

- In the previous expression, only if VBC > 0, i.e. in the forward active mode. When in saturation, VBC < 0 and so IC < βIB.

- Q-III and Q-IV

- I agree that in Q-III the gate of the TRIAC works as an emitter whereas in Q-IV it works as a base, but in Q-IV VBE is positive and VBC is positive too: isn't this saturation? Of course, in Q-IV it is saturated from the beginning, while in Q-III it gets saturated "just after" the beginning, but I am not sure that this alone can account for a higher threshold current. I think that most of the reason lies in the distance between the triggering npn transistor and the final current path, which in Q-III is less than in Q-IV: it is known that diffusion accounts for the greatest part of the current in a semiconductor, so my guess is that the electrons injected into the central n-layer tend to return back into the upper p-layer (where they are minority carriers) before reaching the latching region of this operation mode.

- I hope someone finds a reliable source soon in order to clear any doubt. — Vitaltrust (talk) 20:19, 10 May 2012 (UTC)

- If we both agree about something, it is WP:OR, but at least it's likely to be correct. I'd be tempted to Be Bold, stick it in the article (with a leading disclaimer), and wait for corrections. That's temptation, not decision, however; I'm not quite sure what to do. An alternative would be to put the proposed section on the talk page.

- Saturation

- they must have , so they cannot be both in the forward active region Uh.. why the heck not? I'm saying they are both technically in the forward active region, with Vce greater than Vbe. As the device turns on, Vce and Vbe both drop, pulling with it until the condition is met. I do agree that they keep each other turned on, with each one's collector current being the other's base current. (And the Vcb voltages are necessarily equal.)

- Beta

- Um, well if you want to use that definition of beta, then I agree it's more complicated. I was assuming the standard one, not a more complex model that attempts to fit all modes of operation with a model that includes a parameter called beta because it approximates the standard beta at normal currents. In other words, we aren't arguing about any device physics, just about what number to label "beta".

- Q-III and Q-IV

- I agree that in Q-IV, the triggering transistor is in saturation from the beginning; I thought I said that. The difference is that in Q-III, the transistor is almost active (Vbc is small relative to Vbe), while in Q-IV, it is not only nowhere hear saturation, it is actually slightly reverse-biased (Vbc is slightly larger than Vbe). Current gain decreases the lower you drop Vce, so you expect to need more Ib in Q-III than Q-IV to achieve the same Ic which actually triggers the core thyristor.

- 71.41.210.146 (talk) 04:57, 12 May 2012 (UTC)

- If we both agree about something, it is WP:OR, but at least it's likely to be correct. I'd be tempted to Be Bold, stick it in the article (with a leading disclaimer), and wait for corrections. That's temptation, not decision, however; I'm not quite sure what to do. An alternative would be to put the proposed section on the talk page.

More info is at http://www.st.com/st-web-ui/static/active/en/resource/technical/document/application_note/CD00266635.pdf covering basic TRIAC Control, and a bit of information on the different quadrants. It should help explain a bit, and be a good link to the otherwise dead links at the end of the article.

8r455 (talk) 05:53, 4 March 2013 (UTC)

Broken link

In the External links section, the "The TRIAC, basic functionality" is not working. Darkman101 (talk) 10:21, 28 February 2013 (UTC)

In the References section are items 1 thru 6. Item 6 (about a "snubberless" device) seems to be a dead link. I found a replacement (http://www.st.com/st-web-ui/static/active/en/resource/technical/document/datasheet/CD00263568.pdf) and would like to insert it, but in the wiki source edit area, only items 1-3 are visible; items 4-6 are nowhere to be found! How can that happen? jimswen (talk) 09:40, 9 April 2014 (UTC)

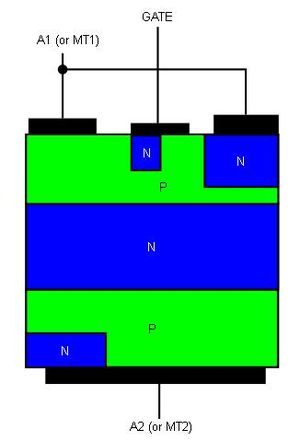

First illustration

The first illustration on the right of the opening section shows MT1 and MT2 as A1 and A2 respectively, but throughout the article the terms MT1 and MT2 are used. Also, MT1 and MT2 are more generally used. Suggest to simplify, especially for the average reader, that the illustration be change to show MT1 and MT2. Mention can then be made in the text about the alternative identities. CPES (talk) 17:40, 9 October 2015 (UTC)

Although I have done some copy editing of this article, I think it's general balance and structure are good. I found it easy to read and quickly revise how TRIACs work. Even though the illustration showing the 4 quadrants could be bigger, the illustrations are particularly well done and help greatly with the explanation. CPES (talk) 22:17, 9 October 2015 (UTC)

More citiations needed

This article is not cited well. It needs more citations and proof. Tombob51 (talk) 12:31, 7 November 2015 (UTC)

Who and when invented TRIAC?

Who and when invented TRIAC? I have found relevant patent http://www.google.com/patents/US3504241 Are there any earlier patents? — Preceding unsigned comment added by 83.237.28.43 (talk) 17:11, 5 October 2013 (UTC)

- The linked patent shows 1967 as the patent date. I seriously doubt there is anything before that. —EncMstr (talk) 03:23, 12 April 2014 (UTC)

- Pt. No SU238016, first working samples were ready in 1962. Inventor: Vasilenko Valentina Stefanovna. First produced on "Electrostal" factory in Saransk, Russia. http://patents.su/4-238016-simmetrichnyjj-tiristor-s-tokom-upravleniya-lyubojj-polyarnosti.html — Preceding unsigned comment added by 46.188.49.203 (talk) 21:58, 3 January 2017 (UTC)