7 nm process

This article may be too technical for most readers to understand. (January 2020) |

| Semiconductor device fabrication |

|---|

|

|

MOSFET scaling (process nodes) |

|

Future

|

This article may rely excessively on sources too closely associated with the subject, potentially preventing the article from being verifiable and neutral. (September 2024) |

In semiconductor manufacturing, the "7 nm" process is a term for the MOSFET technology node following the "10 nm" node, defined by the International Roadmap for Devices and Systems (IRDS), which was preceded by the International Technology Roadmap for Semiconductors (ITRS). It is based on FinFET (fin field-effect transistor) technology, a type of multi-gate MOSFET technology.

As of 2021, the IRDS Lithography standard gives a table of dimensions for the "7 nm" node,[1] with examples given below:

| Calculated Value | nm |

|---|---|

| Minimum half pitch (DRAM, MPU metal) | 18 |

| Minimum half pitch (Flash, MPU fin, LGAA) | 15 |

| Minimum required overlay (OL) (DRAM, Flash, MPU) | 3.6 |

| Gate pitch | 54 |

| Gate length | 20 |

The 2021 IRDS Lithography standard is a retrospective document, as the first volume production of a "7 nm" branded process was in 2016 with Taiwan Semiconductor Manufacturing Company's (TSMC) production of 256Mbit SRAM memory chips using a "7nm" process called N7.[2] Samsung started mass production of their "7nm" process (7LPP) devices in 2018.[3] These process nodes had the same approximate transistor density as Intel's "10 nm Enhanced Superfin" node, later rebranded "Intel 7."[4]

Since at least 1997, the length scale of a process node has not referred to any particular dimension on the integrated circuits, such as gate length, metal pitch, or gate pitch, as new lithography processes no longer uniformly shrank all features on a chip. By the late 2010s, the length scale had become a commercial name[5] that indicated a new generation of process technologies, without any relation to physical properties.[6][7][8] Previous ITRS and IRDS standards had insufficient guidance on process node naming conventions to address the widely varying dimensions on a chip, leading to a divergence between how foundries branded their lithography and the actual dimensions their process nodes achieved.

The first mainstream "7nm" mobile processor intended for mass market use, the Apple A12 Bionic, was announced at Apple's September 2018 event.[9] Although Huawei announced its own "7nm" processor before the Apple A12 Bionic, the Kirin 980 on August 31, 2018, the Apple A12 Bionic was released for public, mass market use to consumers before the Kirin 980. Both chips were manufactured by TSMC.[10]

In 2019,[11] AMD released their "Rome" (EPYC 2) processors for servers and datacenters, which are based on TSMC's N7 node[12] and feature up to 64 cores and 128 threads. They also released their "Matisse" consumer desktop processors with up to 16 cores and 32 threads. However, the I/O die on the Rome multi-chip module (MCM) is fabricated with the GlobalFoundries' 14nm (14HP) process, while the Matisse's I/O die uses the GlobalFoundries' "12nm" (12LP+) process. The Radeon RX 5000 series is also based on TSMC's N7 process.

History

[edit]Technology Demonstrations

[edit]In the early 2000s, researchers began demonstrating 7nm level MOSFETs , with an IBM team including Bruce Doris, Omer Dokumaci, Meikei Ieong, and Anda Mocuta successfully fabricating a 6nm silicon-on-insulator (SOI) MOSFET.[13][14] Shortly after, in 2003, NEC's researchers Hitoshi Wakabayashi and Shigeharu Yamagami advanced further by fabricating a 5nm MOSFET.[15][16]

In July 2015, IBM announced that they had built the first functional transistors with "7nm" technology, using a silicon-germanium process.[17][18][19][20] With further development in February 2017, TSMC produced 256Mbit SRAM memory cells at with their "7nm" process, with a cell area of 0.027 square micrometers,[21] giving a square minimum feature size:

Cumulating in TSMC starting volume of this 7nm production in 2018.[2]

Expected commercialization and technologies

[edit]In 2015, Intel expected that at the 7nm node, III-V semiconductors would have to be used in transistors, signaling a shift away from silicon.[22]

In April 2016, TSMC announced that "7nm" trial production would begin in the first half of 2017.[23] In April 2017, TSMC began risk production of 256Mbit SRAM memory chips using a "7nm" (N7FF+) process,[2] with extreme ultraviolet lithography (EUV).[24] TSMC's "7nm" production plans, as of early 2017,[needs update] was to use deep ultraviolet (DUV) immersion lithography initially on this process node (N7FF), and transition from risk to commercial volume manufacturing from Q2 2017 to Q2 2018. Also, their later generation "7nm" (N7FF+) production was planned[needs update] to use EUV multiple patterning and have an estimated transition from risk to volume manufacturing between 2018 and 2019.[25]

In September 2016, GlobalFoundries announced trial production in the second half of 2017 and risk production in early 2018, with test chips already running.[26]

In February 2017, Intel announced Fab 42 in Chandler, Arizona, which was according to press releases at that time expected[needs update] to produce microprocessors using a "7nm" (Intel 4[27]) manufacturing process.[28] The company had not, at that time, published any expected values for feature lengths at this process node.[needs update]

In April 2018, TSMC announced volume production of "7nm" (CLN7FF, N7) chips. In June 2018, the company announced mass production ramp up.[3]

In May 2018, Samsung announced production of "7nm" (7LPP) chips this year. ASML Holding NV is their main supplier of EUV lithography machines.[29]

In August 2018, GlobalFoundries announced it was stopping development of "7nm" chips, citing cost.[30]

On October 28, 2018, Samsung announced their second generation "7nm" process (7LPP) had entered risk production and was at that time expected to have entered mass production by 2019.[needs update]

On January 17, 2019, for the Q4 2018 earnings call, TSMC mentioned that different customers would have "different flavors" of second generation "7nm".[31][needs update]

On April 16, 2019, TSMC announced their "6nm" process called (CLN6FF, N6), which was, according to a press release made on April 16, 2019, at that time expected to have been in mass products from 2021.[32][needs update] N6 was at that time expected to have used EUVL in up to 5 layers, compared to up to 4 layers in their N7+ process.[33]

On July 28, 2019, TSMC announced their second gen "7nm" process called N7P, which was projected to have been DUV-based like their N7 process.[34] Since N7P was fully IP-compatible with the original "7nm", while N7+ (which uses EUV) was not, N7+ (announced earlier as "7nm+") was to have been a separate process from "7nm". N6 ("6nm"), another EUV-based process, was at that time planned to have been released later than even TSMC's "5nm" (N5) process, with the IP-compatibility with N7. At their Q1 2019 earnings call, TSMC reiterated their Q4 2018 statement[31] that N7+ was at that time expected to have generated less than $1 billion TWD in revenue in 2019.[35][needs update]

On October 5, 2019, AMD announced their EPYC Roadmap, featuring Milan chips built using TSMC's N7+ process.[36][needs update]

On October 7, 2019, TSMC announced they had started delivering N7+ products to market in high volume.[37][needs update]

On July 26, 2021, Intel announced their new manufacturing roadmap, renaming all of their future process nodes.[27] Intel's "10nm" Enhanced SuperFin (10ESF), which was roughly equivalent to TSMC's N7 process, would thenceforth be known as "Intel 7", while their earlier "7nm" process would erstwhile be called "Intel 4".[27][38] As a result, Intel's first processors based on Intel 7 were at that time planned to have started shipping by the second half of 2022,[needs update] whereas Intel announced earlier that they were planning to have launched "7nm" processors in 2023.[39][needs update]

Technology commercialization

[edit]In June 2018, AMD announced 7nm Radeon Instinct GPUs launching in the second half of 2018.[40] In August 2018, the company confirmed the release of the GPUs.[41]

On August 21, 2018, Huawei announced their HiSilicon Kirin 980 SoC to be used in their Huawei Mate 20 and Mate 20 Pro built using TSMC's 7nm (N7) process.[needs update]

On September 12, 2018, Apple announced their A12 Bionic chip used in iPhone XS and iPhone XR built using TSMC's 7nm (N7) process. The A12 processor became the first 7nm chip for mass market use as it released before the Huawei Mate 20.[42][43] On October 30, 2018, Apple announced their A12X Bionic chip used in iPad Pro built using TSMC's 7nm (N7) process.[44]

On December 4, 2018, Qualcomm announced their Snapdragon 855 and 8cx built using TSMC's 7nm (N7) process.[45] The first mass product featuring the Snapdragon 855 was the Lenovo Z5 Pro GT, which was announced on December 18, 2018.[46]

On May 29, 2019, MediaTek announced their 5G SoC built using a TSMC 7nm process.[47]

On July 7, 2019, AMD officially launched their Ryzen 3000 series of central processing units, based on the TSMC 7nm process and Zen 2 microarchitecture.

On August 6, 2019, Samsung announced their Exynos 9825 SoC, the first chip built using their 7LPP process. The Exynos 9825 is the first mass market chip built featuring EUVL.[48]

On September 6, 2019, Huawei announced their HiSilicon Kirin 990 4G & 990 5G SoCs, built using TSMC's N7 and N7+ processes.[49]

On September 10, 2019, Apple announced their A13 Bionic chip used in iPhone 11 and iPhone 11 Pro built using TSMC's 2nd gen N7P process.[50]

7nm (N7 nodes) manufacturing made up 36% of TSMC's revenue in the second quarter of 2020.[51]

On August 17, 2020, IBM announced their Power10 processor.[50]

On July 26, 2021, Intel announced that their Alder Lake processors would be manufactured using their newly rebranded "Intel 7" process, previously known as "10nm Enhanced SuperFin".[27] These processors were, at that time, expected based on press releases to have been planned to have been released in the second half of 2021.[needs update] The company earlier confirmed a 7nm, now called "Intel 4",[27] microprocessor family called Meteor Lake to be released in 2023.[52][53][needs update]

Patterning difficulties

[edit]

The "7nm" foundry node is expected to utilize any of or a combination of the following patterning technologies: pitch splitting, self-aligned patterning, and EUV lithography. Each of these technologies carries significant challenges in critical dimension (CD) control as well as pattern placement, all involving neighboring features.

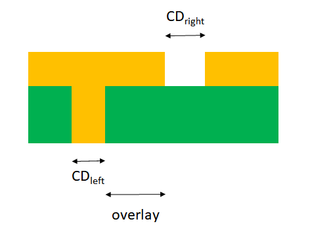

Pitch splitting

[edit]Pitch splitting involves splitting features that are too close together onto different masks, which are exposed successively, followed by litho-etch processing. Due to the use of different exposures, there is always the risk of overlay error between the two exposures, as well as different CDs resulting from the different exposures.

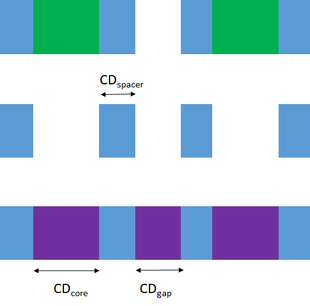

Spacer patterning

[edit]Spacer patterning involves depositing a layer onto pre-patterned features, then etching back to form spacers on the sidewalls of those features, referred to as core features. After removing the core features, the spacers are used as an etch mask to define trenches in the underlying layer. While the spacer CD control is generally excellent, the trench CD may fall into one of two populations, due to the two possibilities of being located where a core feature was located or in the remaining gap. This is known as 'pitch walking'.[54] Generally, pitch = core CD + gap CD + 2 * spacer CD, but this does not guarantee core CD = gap CD. For FEOL features like gate or active area isolation (e.g. fins), the trench CD is not as critical as the spacer-defined CD, in which case, spacer patterning is actually the preferred patterning approach.

When self-aligned quadruple patterning (SAQP) is used, there is a second spacer that is utilized, replacing the first one. In this case, the core CD is replaced by core CD - 2* 2nd spacer CD, and the gap CD is replaced by gap CD - 2 * 2nd spacer CD. Thus, some feature dimensions are strictly defined by the second spacer CD, while the remaining feature dimensions are defined by the core CD, core pitch, and first and second spacer CD's. The core CD and core pitch are defined by conventional lithography, while the spacer CDs are independent of lithography. This is actually expected to have less variation than pitch splitting, where an additional exposure defines its own CD, both directly and through overlay.

Spacer-defined lines also require cutting. The cut spots may shift at exposure, resulting in distorted line ends or intrusions into adjacent lines.

Self-aligned litho-etch-litho-etch (SALELE) has been implemented for "7nm" BEOL patterning.[55]

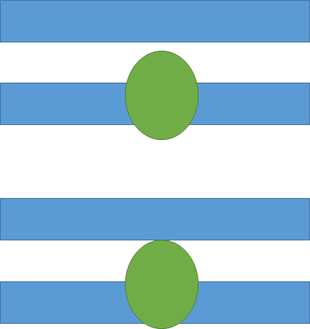

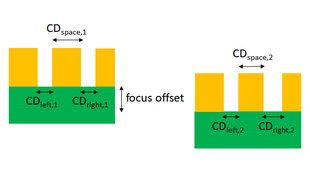

EUV lithography

[edit]Extreme ultraviolet lithography (also known as EUV or EUVL) is capable of resolving features below 20nm in conventional lithography style. However, the 3D reflective nature of the EUV mask results in new anomalies in the imaging. One particular nuisance is the two-bar effect, where a pair of identical bar-shaped features do not focus identically. One feature is essentially in the 'shadow' of the other. Consequently, the two features generally have different CDs which change through focus, and these features also shift position through focus.[56][57][58] This effect may be similar to what may be encountered with pitch splitting. A related issue is the difference of best focus among features of different pitches.[59]

EUV also has issues with reliably printing all features in a large population; some contacts may be completely missing or lines bridged. These are known as stochastic printing failures.[60][61] The defect level is on the order of 1K/mm2.[62]

The tip-to-tip gap is hard to control for EUV, largely due to the illumination constraint.[63] A separate exposure(s) for cutting lines is preferred.

Attenuated phase shift masks have been used in production for 90 nm node for adequate focus windows for arbitrarily pitched contacts with the ArF laser wavelength (193nm),[64][65] whereas this resolution enhancement is not available for EUV.[66][67]

At 2021 SPIE's EUV Lithography conference, it was reported by a TSMC customer that EUV contact yield was comparable to immersion multipatterning yield.[68]

Comparison with previous nodes

[edit]Due to these challenges, "7nm" poses unprecedented patterning difficulty in the back end of line (BEOL). The previous high-volume, long-lived foundry node (Samsung "10nm", TSMC "16nm") used pitch splitting for the tighter pitch metal layers.[69][70][71]

Cycle time: immersion vs. EUV

[edit]| Process | Immersion (≥ 275 WPH)[72] | EUV (1500 wafers/day)[73] |

|---|---|---|

| Single-patterned layer: 1 day completion by immersion |

6000 wafers/day | 1500 wafers/day |

| Double-patterned layer: 2 days completion by immersion |

6000 wafers/2 days | 3000 wafers/2 days |

| Triple-patterned layer: 3 days completion by immersion |

6000 wafers/3 days | 4500 wafers/3 days |

| Quad-patterned layer: 4 days completion by immersion |

6000 wafers/4 days | 6000 wafers/4 days |

Due to the immersion tools being faster presently, multipatterning is still used on most layers. On the layers requiring immersion quad-patterning, the layer completion throughput by EUV is comparable. On the other layers, immersion would be more productive at completing the layer even with multipatterning.

Design rule management in volume production

[edit]The "7nm" metal patterning currently practiced by TSMC involves self-aligned double patterning (SADP) lines with cuts inserted within a cell on a separate mask as needed to reduce cell height.[74] However, self-aligned quad patterning (SAQP) is used to form the fin, the most important factor to performance.[75] Design rule checks also allow via multi-patterning to be avoided, and provide enough clearances for cuts that only one cut mask is needed.[75]

Process nodes and process offerings

[edit]This section's factual accuracy is disputed. (September 2023) |

The naming of process nodes by 4 different manufacturers (TSMC, Samsung, SMIC, Intel) is partially marketing-driven and not directly related to any measurable distance on a chip – for example TSMC's "7nm" node was previously similar in some key dimensions to Intel's planned first-iteration "10nm" node, before Intel released further iterations, culminating in "10nm Enhanced SuperFin", which was later renamed to "Intel 7" for marketing reasons.[76][77]

Since EUV implementation at "7nm" is still limited, multipatterning still plays an important part in cost and yield; EUV adds extra considerations. The resolution for most critical layers is still determined by multiple patterning. For example, for Samsung's "7nm", even with EUV single-patterned 36nm pitch layers, 44nm pitch layers would still be quadruple patterned.[78]

| Samsung | TSMC | Intel | SMIC | |||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Process name | 7LPP[79][80] | 6LPP[81] | N7[82] | N7P[34] | N7+[83] | N6 | Intel 7[27][disputed – discuss] (10nm)[84] | N+1 (>7nm) | N+2 (7nm) | 7nm EUV |

| Transistor density (MTr/mm2) | 95.08–100.59[85][86] | Unknown | 91.2–96.5[87][88] | 113.9[87] | 114.2[32] | 100.76–106.1[89][90] 60.41[91] | 89[92] | Unknown | Unknown | |

| SRAM bit-cell size | 0.0262 μm2[93] | Unknown | 0.027 μm2[93] | Unknown | Unknown | 0.0312 μm2 | Unknown | Unknown | Unknown | |

| Transistor gate pitch | 54nm | Unknown | 57nm | 54nm | 66nm | 63nm | Unknown | |||

| Transistor fin pitch | 27nm | Unknown | N/A | Unknown | Unknown | 34nm | Unknown | Unknown | Unknown | |

| Transistor fin height | Unknown | Unknown | N/A | Unknown | Unknown | 53nm | Unknown | Unknown | Unknown | |

| Minimum (metal) pitch | 46nm | Unknown | 40nm | 40nm[94] | 44nm | 42nm | Unknown | |||

| EUV implementation | 36nm pitch metal;[78] 20% of total layer set |

Unknown | None, used self-aligned quad patterning (SAQP) instead | 4 layers | 5 layers | None. Relied on SAQP heavily | None | None | Yes (after N+2) | |

| EUV-limited wafer output | 1500 wafers/day[73] | Unknown | N/A | ~ 1000 wafers/day[95] | Unknown | N/A | Unknown | Unknown | Unknown | |

| Multipatterning (≥ 2 masks on a layer) |

Fins Gate Vias (double-patterned)[96] Metal 1 (triple-patterned)[96] 44nm pitch metal (quad-patterned)[78] |

Unknown | Fins Gate Contacts/vias (quad-patterned)[97] Lowest 10 metal layers |

Same as N7, with reduction on 4 EUV layers | Same as N7, with reduction on 5 EUV layers | multipatterning with DUV | multipatterning with DUV | Unknown | ||

| Release status | 2018 risk production 2019 production |

2020 production | 2017 risk production 2018 production[2] |

2019 production | 2018 risk production[2] 2019 production |

2020 risk production 2020 production |

2021 production[27] | April 2021 risk production, mass production unknown | Late 2021 risk production, quietly produced since July 2021[98] | Cancelled due to US embargo |

GlobalFoundries' "7nm" 7LP (Leading Performance) process would have offered 40% higher performance or 60%+ lower power with a 2x scaling in density and at a 30-45+% lower cost per die over its "14nm" process. The Contacted Poly Pitch (CPP) would have been 56nm and the Minimum Metal Pitch (MMP) would have been 40nm, produced with Self-Aligned Double Patterning (SADP). A 6T SRAM cell would have been 0.269 square microns in size. GlobalFoundries planned to eventually use EUV lithography in an improved process called 7LP+.[99] GlobalFoundries later stopped all "7nm" and beyond process development.[100]

Intel's new "Intel 7" process, previously known as "10nm Enhanced SuperFin" (10ESF), is based on its previous "10nm" node. The node will feature a 10-15% increase in performance per watt. Meanwhile, their old "7nm" process, now called "Intel 4", was at that time expected to have been released in 2023.[101][needs update] Few details about the "Intel 4" node had at that time been made public, although its transistor density had at that time been estimated to be at least 202 million transistors per square millimeter.[27][102][needs update] As of 2020, Intel had been experiencing problems with its "Intel 4" process to the point of outsourcing production of its Ponte Vecchio GPUs.[103][104][needs update]

References

[edit]- ^ "International Roadmap for Devices and Systems 2021 Update: Lithography" (PDF). International Roadmap for Devices and Systems. 7 April 2024.

- ^ a b c d e "7nm Technology". TSMC. Retrieved June 30, 2019.

- ^ a b Chen, Monica; Shen, Jessie (22 June 2018). "TSMC ramping up 7nm chip production". DigiTimes. Retrieved September 17, 2022.

- ^ Subramaniam, Vaidyanathan (27 July 2021). "Intel details new process innovations and node names, Alder Lake 10 nm Enhanced SuperFin is now Intel 7; Intel 20A is the 2 nm process for 2024". Notebook Check.

- ^ Morris, Kevin (July 23, 2020). "No More Nanometers: It's Time for New Node Naming". Electronic Engineering Journal. Retrieved September 17, 2022.

- ^ Shukla, Priyank. "A Brief History of Process Node Evolution". Design-Reuse. Retrieved July 9, 2019.

- ^ Hruska, Joel (June 23, 2014). "14nm, 7nm, 5nm: How low can CMOS go? It depends if you ask the engineers or the economists…". ExtremeTech. Retrieved September 17, 2022.

- ^ Pirzada, Usman (September 16, 2016). "Exclusive: Is Intel Really Starting To Lose Its Process Lead? 7nm Node Slated For Release in 2022". Wccftech. Retrieved September 17, 2022.

- ^ Shankland, Stephen (September 12, 2018). "Apple's A12 Bionic CPU for the new iPhone XS is ahead of the industry moving to 7nm chip manufacturing tech". CNET. Retrieved September 16, 2018.

- ^ Summers, N. (September 12, 2018). "Apple's A12 Bionic is the first 7-nanometer smartphone chip". Engadget. Retrieved September 20, 2018.

- ^ "AMD Launches Epyc Rome, First 7nm CPU". August 8, 2019. Archived from the original on 2019-08-15.

- ^ Smith, Ryan (July 26, 2018). "AMD "Rome" EPYC CPUs to Be Fabbed By TSMC". AnandTech. Retrieved 18 June 2019.

- ^ "IBM claims world's smallest silicon transistor - TheINQUIRER". Theinquirer.net. 2002-12-09. Archived from the original on May 31, 2011. Retrieved 7 December 2017.

- ^ Doris, Bruce B.; Dokumaci, Omer H.; Ieong, Meikei K.; Mocuta, Anda; Zhang, Ying; Kanarsky, Thomas S.; Roy, R. A. (December 2002). "Extreme scaling with ultra-thin Si channel MOSFETs". Digest. International Electron Devices Meeting. pp. 267–270. doi:10.1109/IEDM.2002.1175829. ISBN 0-7803-7462-2. S2CID 10151651.

- ^ "NEC test-produces world's smallest transistor". The Free Library. Retrieved December 7, 2017.

- ^ Wakabayashi, Hitoshi; Yamagami, Shigeharu; Ikezawa, Nobuyuki; Ogura, Atsushi; Narihiro, Mitsuru; Arai, K.; Ochiai, Y.; Takeuchi, K.; Yamamoto, T.; Mogami, T. (December 2003). "Sub-10-nm planar-bulk-CMOS devices using lateral junction control". IEEE International Electron Devices Meeting 2003. pp. 20.7.1–20.7.3. doi:10.1109/IEDM.2003.1269446. ISBN 0-7803-7872-5. S2CID 2100267.

- ^ Dignan, Larry. "IBM Research builds functional 7nm processor". ZDNet.

- ^ Markoff, John (July 9, 2015). "IBM Discloses Working Version of a Much Higher-Capacity Chip". The New York Times.

- ^ "Beyond silicon: IBM unveils world's first 7nm chip – Ars Technica". arstechnica.com. July 9, 2015.

- ^ "Seven Advancements for Beyond 7nm Chips". IBM Research Blog. February 27, 2017.

- ^ Chang, J.; Chen, Y.; Chan, W.; Singh, S. P.; Cheng, H.; Fujiwara, H.; Lin, J.; Lin, K.; Hung, J.; Lee, R.; Liao, H. (February 2017). "12.1 a 7nm 256Mb SRAM in high-k metal-gate FinFET technology with write-assist circuitry for low-VMIN applications". 2017 IEEE International Solid-State Circuits Conference (ISSCC). pp. 206–207. doi:10.1109/ISSCC.2017.7870333. ISBN 978-1-5090-3758-2. S2CID 19930825.

- ^ "Intel forges ahead to 10nm, will move away from silicon at 7nm". February 23, 2015.

- ^ Parish, Kevin (April 20, 2016). "Watch out Intel and Samsung: TSMC is gearing up for 7 nm processing with trial production". Digital Trends. Retrieved September 17, 2022.

- ^ "TSMC Tips 7+, 12, 22nm Nodes | EE Times". EETimes. Retrieved 2017-03-17.

- ^ Shilov, Anton (5 May 2017). "Samsung and TSMC Roadmaps: 8 and 6 nm Added, Looking at 22ULP and 12FFC". AnandTech. Retrieved September 17, 2022.

- ^ "GLOBALFOUNDRIES to Deliver Industry's Leading-Performance Offering of 7 nm FinFET Technology". GlobalFoundries (Press release). September 15, 2016. Retrieved April 8, 2017.

- ^ a b c d e f g h Cutress, Ian. "Intel's Process Roadmap to 2025: with 4nm, 3nm, 20A and 18A?!". www.anandtech.com. Retrieved 2021-07-27.

- ^ "Intel Supports American Innovation with $7 Billion Investment in Next-Generation Semiconductor Factory in Arizona". Intel Newsroom. February 8, 2017. Retrieved September 17, 2022.

- ^ King, Ian (May 22, 2018). "Samsung Says New 7-Nanometer Chip Production Starting This Year". Bloomberg. Retrieved September 17, 2022.

- ^ Dent, Steve (August 28, 2018). "Major AMD chip supplier will no longer make next-gen chips". Engadget. Retrieved September 17, 2022.

- ^ a b Q4 2018 TSMC earnings call transcript, January 17, 2019.

- ^ a b Schor, David (April 16, 2019). "TSMC Announces 6-Nanometer Process". WikiChip Fuse. Retrieved May 31, 2019.

- ^ Shilov, Anton (May 1, 2019). "TSMC: Most 7nm Clients Will Transition to 6nm". AnandTech. Retrieved May 31, 2019.

- ^ a b Schor, David (July 28, 2019). "TSMC Talks 7nm, 5nm, Yield, And Next-Gen 5G And HPC Packaging". WikiChip Fuse. Retrieved September 13, 2019.

- ^ C. C. Wei, TSMC Q1 2019 earnings call (April 18) transcript.

- ^ Alcorn, Paul (October 5, 2019). "AMD Dishes on Zen 3 and Zen 4 Architecture, Milan and Genoa Roadmap". Tom's Hardware. Retrieved October 8, 2019.

- ^ "TSMC's N7+ Technology is First EUV Process Delivering Customer Products to Market in High Volume | Planet 3DNow!" (in German). October 7, 2019. Retrieved 2019-10-08.

- ^ "Accelerating Process Innovation" (PDF). Intel. July 26, 2021.

- ^ Jones, Ryan (March 27, 2021). "Ctrl+Alt+Delete: Why you should be excited for Intel's 7nm processor". Trusted Reviews. Retrieved March 30, 2021.

- ^ "Pushing Boundaries for CPUs and GPUs, AMD Shows Next-Generation of Ryzen, Radeon and EPYC Product Leadership at Computex 2018" (Press release). June 5, 2018.

- ^ Martin, Dylan (August 23, 2018). "AMD CTO: 'We Went All In' On 7nm CPUs". CRN. Retrieved September 17, 2022.

- ^ "Apple Announces 'iPhone Xs' and 'iPhone Xs Max' With Gold Color, Faster Face ID, and More". September 12, 2018.

- ^ Freedman, Andrew E. (September 12, 2018). "Apple Introduces 7nm A12 Bionic CPU for iPhone XS". Tom's Hardware. Retrieved September 12, 2018.

- ^ Axon, Samuel (November 7, 2018). "Apple walks Ars through the iPad Pro's A12X system on a chip". Ars Technica. Retrieved November 18, 2018.

- ^ Cutress, Ian (December 4, 2018). "Qualcomm Tech Summit, Day 1: Announcing 5G Partnerships and Snapdragon 855". AnandTech. Retrieved May 31, 2019.

- ^ Frumusanu, Andrei (December 18, 2018). "Lenovo First to a Snapdragon 855 Phone with Announcement of Z5 Pro GT". AnandTech. Retrieved May 31, 2019.

- ^ "MediaTek 5G". MediaTek. Retrieved May 31, 2019.

- ^ Siddiqui, Aamir (August 7, 2019). "Samsung announces Exynos 9825 prior to Galaxy Note 10 launch". XDA-Developers. Retrieved September 13, 2019.

- ^ Cutress, Ian. "Huawei Announces Kirin 990 and Kirin 990 5G: Dual SoC Approach, Integrated 5G Modem". AnandTech. Retrieved September 13, 2019.

- ^ a b "IBM Reveals Next-Generation IBM POWER10 Processor". IBM Newsroom. August 17, 2020. Retrieved August 17, 2020.

- ^ "TSMC Plots an Aggressive Course for 3nm Lithography and Beyond - ExtremeTech".

- ^ "Intel CEO Announces 'IDM 2.0' Strategy for Manufacturing, Innovation". Intel Newsroom. March 23, 2021. Retrieved September 17, 2022.

- ^ "Intel Unleashed: Engineering the Future (Replay)". Intel Newsroom. March 23, 2021. Retrieved September 17, 2022.

- ^ M. J. Maslow et al., Proc. SPIE 10587, 1058704 (2018).

- ^ SALELE Double Patterning for 7nm and 5nm Nodes

- ^ "IMEC EUVL 2018 Workshop" (PDF).

- ^ Y. Nakajima et al., EUVL Symposium 2007, Sapporo.

- ^ L. de Winter et al., Proc. SPIE 9661, 96610A (2015).

- ^ M. Burkhardt and A. Raghunathan, Proc. SPIE 9422, 94220X (2015).

- ^ P. De Bisschop and E. Hendrickx, Proc. SPIE 10583, 105831K (2018).

- ^ "EUV's Stochastic Valley of Death". linkedin.com.

- ^ S. Larivière et al., Proc. SPIE 10583, 105830U (2018).

- ^ E. van Setten et al., Proc. SPIE 9661. 96610G (2015).

- ^ C-H. Chang et al., Proc. SPIE 5377, 902 (2004).

- ^ T. Devoivre et al., MTDT 2002.

- ^ S-S. Yu et al., Proc. SPIE 8679, 86791L (2013).

- ^ A. Erdmann et al., Proc. SPIE 10583, 1058312 (2018).

- ^ Qi Li et al., Proc. SPIE 11609, 116090V (2021).

- ^ Jeong, W. C.; Ahn, J. H.; Bang, Y. S.; Yoon, Y. S.; Choi, J. Y.; Kim, Y. C.; Paek, S. W.; Ahn, S. W.; Kim, B. S.; Song, T. J.; Jung, J. H.; Do, J. H.; Lim, S. M.; Cho, H.-; Lee, J. H.; Kim, D. W.; Kang, S. B.; Ku, J.-; Kwon, S. D.; Jung, S.-; Yoon, J. S. (June 23, 2017). "10nm 2nd generation BEOL technology with optimized illumination and LELELELE". 2017 Symposium on VLSI Technology. pp. T144–T145. doi:10.23919/VLSIT.2017.7998156. ISBN 978-4-86348-605-8. S2CID 43207918 – via IEEE Xplore.

- ^ "TSMC Symposium: "10nm is Ready for Design Starts at This Moment" - Industry Insights - Cadence Blogs - Cadence Community". community.cadence.com.

- ^ Wu, S.; Lin, C. Y.; Chiang, M. C.; Liaw, J. J.; Cheng, J. Y.; Yang, S. H.; Liang, M.; Miyashita, T.; Tsai, C. H.; Hsu, B. C.; Chen, H. Y.; Yamamoto, T.; Chang, S. Y.; Chang, V. S.; Chang, C. H.; Chen, J. H.; Chen, H. F.; Ting, K. C.; Wu, Y. K.; Pan, K. H.; Tsui, R. F.; Yao, C. H.; Chang, P. R.; Lien, H. M.; Lee, T. L.; Lee, H. M.; Chang, W.; Chang, T.; Chen, R.; Yeh, M.; Chen, C. C.; Chiu, Y. H.; Chen, Y. H.; Huang, H. C.; Lu, Y. C.; Chang, C. W.; Tsai, M. H.; Liu, C. C.; Chen, K. S.; Kuo, C. C.; Lin, H. T.; Jang, S. M.; Ku, Y. (December 23, 2013). "A 16nm FinFET CMOS technology for mobile SoC and computing applications". 2013 IEEE International Electron Devices Meeting. pp. 9.1.1–9.1.4. doi:10.1109/IEDM.2013.6724591. ISBN 978-1-4799-2306-9 – via IEEE Xplore.

- ^ "Products & services - Supplying the semiconductor industry". asml.com.

- ^ a b "Samsung Ramps 7nm EUV Chips". EETimes. October 17, 2018.

- ^ "7 nm lithography process - WikiChip".

- ^ a b "A Heuristic Approach to Fix Design Rule Check (DRC) Violations in ASIC Designs @7nm FinFET Technology". Design And Reuse.

- ^ Merrit, Rick (16 Jan 2017). "15 Views from a Silicon Summit". EETimes. Retrieved September 16, 2022.

- ^ Hill, Brandon (March 28, 2017). "Intel Details Cannonlake's Advanced 10nm FinFET Node, Claims Full Generation Lead Over Rivals". HotHardware. Archived from the original on June 12, 2018. Retrieved August 30, 2018.

- ^ a b c J. Kim et al., Proc. SPIE 10962, 1096204 (2019).

- ^ "VLSI 2018: Samsung's 2nd Gen 7nm, EUV Goes HVM". WikiChip. August 4, 2018. Retrieved September 16, 2022.

- ^ "Samsung Electronics Starts Production of EUV-based 7nm LPP Process". Samsung Newsroom. October 18, 2018. Retrieved September 16, 2022.

- ^ "Samsung Starts Mass Production at V1: A Dedicated EUV Fab for 7nm, 6nm, 5nm, 4nm, 3nm Nodes".

- ^ IEDM 2016

- ^ "TSMC Goes Photon to Cloud". EETimes. October 4, 2018.

- ^ Bonshor, Gavin (20 October 2022). "Intel Core i9-13900K and i5-13600K Review: Raptor Lake Brings More Bite". AnandTech. Retrieved 28 September 2023.

- ^ "Can TSMC Maintain Their Process Technology Lead". July 18, 2023.

- ^ "Samsung 3nm GAAFET Enters Risk Production; Discusses Next-Gen Improvements". July 5, 2022.

- ^ a b Jones, Scotten (May 3, 2019). "TSMC and Samsung 5nm Comparison". Semiwiki. Retrieved 30 July 2019.

- ^ "N3E Replaces N3; Comes in Many Flavors". September 4, 2022.

- ^ Jones, Scotten (July 18, 2023), Can TSMC Maintain Their Process Technology Lead

- ^ "Intel's Process Roadmap to 2025: With 4nm, 3nm, 20A and 18A?!".

- ^ Schor, David (2022-06-19). "A Look At Intel 4 Process Technology". WikiChip Fuse.

- ^ SMIC Mass Produces 14nm Nodes, Advances To 5nm, 7nm, September 16, 2022

- ^ a b "VLSI 2018: Samsung's 2nd Gen 7nm, EUV Goes HVM". WikiChip Fuse. 2018-08-04. Retrieved 2019-05-31.

- ^ Smith, Ryan (June 13, 2022). "Intel 4 Process Node In Detail: 2x Density Scaling, 20% Improved Performance". AnandTech. Retrieved September 17, 2022.

- ^ "TSMC Q1 2018 earnings call transcript, p.12" (PDF). Archived from the original (PDF) on October 14, 2018. Retrieved October 14, 2018.

- ^ a b W. C. Jeong et al., VLSI Technology 2017.

- ^ Dillinger, Tom (March 23, 2017). "Top 10 Updates from the TSMC Technology Symposium, Part II". SemiWiki. Retrieved September 16, 2022.

- ^ Paul Alcorn (21 July 2022). "China's SMIC Shipping 7nm Chips, Reportedly Copied TSMC's Tech". Tom's Hardware.

- ^ Jones, Scotten (July 8, 2017). "Exclusive - GLOBALFOUNDRIES discloses 7nm process detail". SemiWiki. Retrieved September 16, 2022.

- ^ Shilov, Anton; Cutress, Ian (August 27, 2018). "GlobalFoundries Stops All 7nm Development: Opts To Focus on Specialized Processes". AnandTech. Retrieved July 27, 2021.

- ^ "Intel: Sorry, But Our 7nm Chips Will Be Delayed to 2022, 2023". PCMAG. Retrieved 2021-07-27.

- ^ "7 nm lithography process - WikiChip".

- ^ "Intel's 7nm Process Six Months Behind Schedule - News".

- ^ "As 7nm schedule continues slipping, Intel contemplates 3rd-party fabs". July 24, 2020.

External links

[edit]| Preceded by 10 nm |

MOSFET semiconductor device fabrication process | Succeeded by 5 nm |