LPDDR

| Computer memory and data storage types |

|---|

| Volatile |

| Non-volatile |

Low-Power Double Data Rate (LPDDR), also known as LPDDR SDRAM, is a type of synchronous dynamic random-access memory (SDRAM) that consumes less power than other random access memory designs and is thus targeted for mobile computing devices such as laptop computers and smartphones. Older variants are also known as Mobile DDR, and abbreviated as mDDR.

Modern LPDDR SDRAM is distinct from DDR SDRAM, with various differences that make the technology more appropriate for mobile applications.[1] LPDDR technology standards are developed independently of DDR standards, with LPDDR4X and even LPDDR5 for example being implemented prior to DDR5 SDRAM and offering far higher data rates than DDR4 SDRAM.

Bus width

[edit]| LPDDR | 1 | 1E | 2 | 2E | 3 | 3E | 4 | 4X | 5 | 5X |

|---|---|---|---|---|---|---|---|---|---|---|

| Maximum data bit width | 32 | 64 | 64 | 32 | 32 | |||||

| Memory array clock (MHz) | 200 | 266 | 200 | 266 | 200 | 266 | 200 | 266 | 400 | 533 |

| Prefetch size | 2n | 4n | 8n | 16n | ||||||

| Memory densities | 64 Mbit – 8 Gbit | 1–32 Gbit | 4–32 Gbit | 4–32 Gbit | ||||||

| I/O bus clock frequency (MHz) | 200 | 266 | 400 | 533 | 800 | 1067 | 1600 | 2133 | 3200 | 4267 |

| Data transfer rate, DDR (MT/s)[a] | 400 | 533 | 800 | 1067 | 1600 | 2133 | 3200 | 4267 | 6400 | 8533 |

| Supply voltages (volts) | 1.8 | 1.2, 1.8 | 1.2, 1.8 | 1.1, 1.8 | 0.6, 1.1, 1.8 | 0.5, 1.05, 1.8 | 0.5, 1.05, 1.8 | |||

| Command/address bus | 19 bits, SDR | 10 bits, DDR | 6 bits, SDR | 7 bits, DDR | ||||||

| Year | 2006 | 2009 | 2012 | 2014 | 2017 | 2019 | 2021 | |||

In contrast with standard SDRAM, used in stationary devices and laptops and usually connected over a 64-bit wide memory bus, LPDDR also permits 16- or 32-bit wide channels.[2]

The "E" and "X" versions mark enhanced versions of the specifications. They formalize overclocking the memory array by usually 33%.

As with standard SDRAM, most generations double the internal fetch size and external transfer speed. (DDR4 and LPDDR5 being the exceptions.)

Generations

[edit]LPDDR(1)

[edit]The original low-power DDR (sometimes retroactively called LPDDR1), released in 2006 is a slightly modified form of DDR SDRAM, with several changes to reduce overall power consumption.

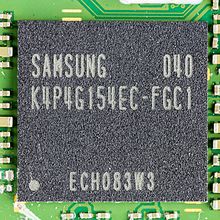

Most significantly, the supply voltage is reduced from 2.5 to 1.8 V. Additional savings come from temperature-compensated refresh (DRAM requires refresh less often at low temperatures), partial array self refresh, and a "deep power down" mode which sacrifices all memory contents. Additionally, chips are smaller, using less board space than their non-mobile equivalents. Samsung and Micron are two of the main providers of this technology, which is used in tablet and phone devices such as the iPhone 3GS, original iPad, Samsung Galaxy Tab 7.0 and Motorola Droid X.[3]

LPDDR2

[edit]

In 2009, the standards group JEDEC published JESD209-2, which defined a more dramatically revised low-power DDR interface.[4][5] It is not compatible with either DDR1 or DDR2 SDRAM, but can accommodate any one of:

- LPDDR2-S2: 2n prefetch memory (like DDR1),

- LPDDR2-S4: 4n prefetch memory (like DDR2), or

- LPDDR2-N: Non-volatile (NAND flash) memory.

Low-power states are similar to basic LPDDR, with some additional partial array refresh options.

Timing parameters are specified for LPDDR-200 to LPDDR-1066 (clock frequencies of 100 to 533 MHz).

Working at 1.2 V, LPDDR2 multiplexes the control and address lines onto a 10-bit double data rate CA bus. The commands are similar to those of normal SDRAM, except for the reassignment of the precharge and burst terminate opcodes:

| Operation | ↗ Rising clock ↗ | ↘ Falling clock ↘ | |||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| CA0 (RAS) |

CA1 (CAS) |

CA2 (WE) |

CA3 |

CA4 |

CA5 |

CA6 |

CA7 |

CA8 |

CA9 |

CA0 (RAS) |

CA1 (CAS) |

CA2 (WE) |

CA3 |

CA4 |

CA5 |

CA6 |

CA7 |

CA8 |

CA9 | ||

| No operation | H | H | H | — | |||||||||||||||||

| Precharge all banks | H | H | L | H | H | — | |||||||||||||||

| Precharge one bank | H | H | L | H | L | — | BA0 | BA1 | BA2 | — | |||||||||||

| Preactive (LPDDR2-N only) | H | H | L | H | A30 | A31 | A32 | BA0 | BA1 | BA2 | A20 | A21 | A22 | A23 | A24 | A25 | A26 | A27 | A28 | A29 | |

| Burst terminate | H | H | L | L | — | ||||||||||||||||

| Read (AP=auto-precharge) | H | L | H | reserved | C1 | C2 | BA0 | BA1 | BA2 | AP | C3 | C4 | C5 | C6 | C7 | C8 | C9 | C10 | C11 | ||

| Write (AP=auto-precharge) | H | L | L | reserved | C1 | C2 | BA0 | BA1 | BA2 | AP | C3 | C4 | C5 | C6 | C7 | C8 | C9 | C10 | C11 | ||

| Activate (R0–14=Row address) | L | H | R8 | R9 | R10 | R11 | R12 | BA0 | BA1 | BA2 | R0 | R1 | R2 | R3 | R4 | R5 | R6 | R7 | R13 | R14 | |

| Activate (LPDDR2-N only) | L | H | A15 | A16 | A17 | A18 | A19 | BA0 | BA1 | BA2 | A5 | A6 | A7 | A8 | A9 | A10 | A11 | A12 | A13 | A14 | |

| Refresh all banks (LPDDR2-Sx only) | L | L | H | H | — | ||||||||||||||||

| Refresh one bank (round-robin addressing) | L | L | H | L | — | ||||||||||||||||

| Mode register read (MA0–7=address) | L | L | L | H | MA0 | MA1 | MA2 | MA3 | MA4 | MA5 | MA6 | MA7 | — | ||||||||

| Mode register write (OP0–7=data) | L | L | L | L | MA0 | MA1 | MA2 | MA3 | MA4 | MA5 | MA6 | MA7 | OP0 | OP1 | OP2 | OP3 | OP4 | OP5 | OP6 | OP7 | |

Column address bit C0 is never transferred, and is assumed to be zero. Burst transfers thus always begin at even addresses.

LPDDR2 also has an active-low chip select (when high, everything is a NOP) and clock enable CKE signal, which operate like SDRAM. Also like SDRAM, the command sent on the cycle that CKE is first dropped selects the power-down state:

- If the chip is active, it freezes in place.

- If the command is a NOP (CS low or CA0–2 = HHH), the chip idles.

- If the command is a refresh command (CA0–2 = LLH), the chip enters the self-refresh state.

- If the command is a burst terminate (CA0–2 = HHL), the chip enters the deep power-down state. (A full reset sequence is required when leaving.)

The mode registers have been greatly expanded compared to conventional SDRAM, with an 8-bit address space, and the ability to read them back. Although smaller than a serial presence detect EEPROM, enough information is included to eliminate the need for one.

S2 devices smaller than 4 Gbit, and S4 devices smaller than 1 Gbit have only four banks. They ignore the BA2 signal, and do not support per-bank refresh.

Non-volatile memory devices do not use the refresh commands, and reassign the precharge command to transfer address bits A20 and up. The low-order bits (A19 and down) are transferred by a following Activate command. This transfers the selected row from the memory array to one of 4 or 8 (selected by the BA bits) row data buffers, where they can be read by a Read command. Unlike DRAM, the bank address bits are not part of the memory address; any address can be transferred to any row data buffer. A row data buffer may be from 32 to 4096 bytes long, depending on the type of memory. Rows larger than 32 bytes ignore some of the low-order address bits in the Activate command. Rows smaller than 4096 bytes ignore some of the high-order address bits in the Read command.

Non-volatile memory does not support the Write command to row data buffers. Rather, a series of control registers in a special address region support Read and Write commands, which can be used to erase and program the memory array.

LPDDR3

[edit]In May 2012, JEDEC published the JESD209-3 Low Power Memory Device Standard.[6][7][8] In comparison to LPDDR2, LPDDR3 offers a higher data rate, greater bandwidth and power efficiency, and higher memory density. LPDDR3 achieves a data rate of 1600 MT/s and utilizes key new technologies: write-leveling and command/address training,[9] optional on-die termination (ODT), and low-I/O capacitance. LPDDR3 supports both package-on-package (PoP) and discrete packaging types.

The command encoding is identical to LPDDR2, using a 10-bit double data rate CA bus.[7] However, the standard only specifies 8n-prefetch DRAM, and does not include the flash memory commands.

Products using LPDDR3 include the 2013 MacBook Air, iPhone 5S, iPhone 6, Nexus 10, Samsung Galaxy S4 (GT-I9500) and Microsoft Surface Pro 3 and 4.[10] LPDDR3 went mainstream in 2013, running at 800 MHz DDR (1600 MT/s), offering bandwidth comparable to PC3-12800 notebook memory in 2011 (12.8 GB/s of bandwidth).[11] To achieve this bandwidth, the controller must implement dual-channel memory. For example, this is the case for the Exynos 5 Dual[12] and the 5 Octa.[13]

LPDDR3E

[edit]An "enhanced" version of the specification called LPDDR3E increases the data rate to 2133 MT/s. Samsung Electronics introduced the first 4 gigabit 20 nm-class LPDDR3 modules capable of transmitting data at up to 2,133 MT/s, more than double the performance of the older LPDDR2 which is only capable of 800 MT/s.[14] Various SoCs from various manufacturers also natively support 800 MHz LPDDR3 RAM. Such include the Snapdragon 600 and 800 from Qualcomm[15] as well as some SoCs from the Exynos and Allwinner series.

LPDDR4

[edit]On 14 March 2012, JEDEC hosted a conference to explore how future mobile device requirements will drive upcoming standards like LPDDR4.[16] On 30 December 2013, Samsung announced that it had developed the first 20 nm-class 8 gigabit (1 GB) LPDDR4 capable of transmitting data at 3,200 MT/s, thus providing 50 percent higher performance than the fastest LPDDR3 and consuming around 40 percent less energy at 1.1 volts.[17][18]

On 25 August 2014, JEDEC published the JESD209-4 LPDDR4 Low Power Memory Device Standard.[19][20]

Significant changes include:

- Doubling of the interface speed, and numerous consequent electrical changes, including changing the I/O standard to low-voltage swing-terminated logic (LVSTL)

- Doubling of the internal prefetch size, and minimum transfer size

- Change from a 10-bit DDR command/address bus to a 6-bit SDR bus

- Change from one 32-bit wide bus to two independent 16-bit wide buses

- Self-refresh is enabled by dedicated commands, rather than being controlled by the CKE line

The standard defines SDRAM packages containing two independent 16-bit access channels, each connected to up to two dies per package. Each channel is 16 data bits wide, has its own control/address pins, and allows access to 8 banks of DRAM. Thus, the package may be connected in three ways:

- Data lines and control connected in parallel to a 16-bit data bus, and only chip selects connected independently per channel.

- To two halves of a 32-bit wide data bus, and the control lines in parallel, including chip select.

- To two independent 16-bit wide data buses

Each die provides 4, 6, 8, 12, or 16 gigabits of memory, half to each channel. Thus, each bank is one sixteenth the device size. This is organized into the appropriate number (16 K to 64 K) of 16384-bit (2048-byte) rows. Extension to 24 and 32 gigabits is planned, but it is not yet decided if this will be done by increasing the number of rows, their width, or the number of banks.

Larger packages providing double width (four channels) and up to four dies per pair of channels (8 dies total per package) are also defined.

Data is accessed in bursts of either 16 or 32 transfers (256 or 512 bits, 32 or 64 bytes, 8 or 16 cycles DDR). Bursts must begin on 64-bit boundaries.

Since the clock frequency is higher and the minimum burst length longer than earlier standards, control signals can be more highly multiplexed without the command/address bus becoming a bottleneck. LPDDR4 multiplexes the control and address lines onto a 6-bit single data rate CA bus. Commands require 2 clock cycles, and operations encoding an address (e.g., activate row, read or write column) require two commands. For example, to request a read from an idle chip requires four commands taking 8 clock cycles: Activate-1, Activate-2, Read, CAS-2.

The chip select line (CS) is active-high. The first cycle of a command is identified by chip select being high; it is low during the second cycle.

| First cycle (CS high) | Second cycle (CS low) | Operation | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| CA5 | CA4 | CA3 | CA2 | CA1 | CA0 | CA5 | CA4 | CA3 | CA2 | CA1 | CA0 | |||

| L | L | L | L | L | L | — | No operation | |||||||

| H | L | L | L | L | L | 0 | OP4 | OP3 | OP2 | OP1 | 1 | Multi-purpose command | ||

| AB | H | L | L | L | L | — | BA2 | BA1 | BA0 | Precharge (AB: all banks) | ||||

| AB | L | H | L | L | L | — | BA2 | BA1 | BA0 | Refresh (AB: all banks) | ||||

| — | H | H | L | L | L | — | Self-refresh entry | |||||||

| BL | L | L | H | L | L | AP | C9 | — | BA2 | BA1 | BA0 | Write-1 (+CAS-2) | ||

| — | H | L | H | L | L | — | Self-refresh exit | |||||||

| 0 | L | H | H | L | L | AP | C9 | — | BA2 | BA1 | BA0 | Masked write-1 (+CAS-2) | ||

| — | H | H | H | L | L | — | Reserved | |||||||

| BL | L | L | L | H | L | AP | C9 | — | BA2 | BA1 | BA0 | Read-1 (+CAS-2) | ||

| C8 | H | L | L | H | L | C7 | C6 | C5 | C4 | C3 | C2 | CAS-2 | ||

| — | H | L | H | L | — | Reserved | ||||||||

| OP7 | L | L | H | H | L | MA5 | MA4 | MA3 | MA2 | MA1 | MA0 | Mode register write-1 and -2 MA: address, OP: data | ||

| OP6 | H | L | H | H | L | OP5 | OP4 | OP3 | OP2 | OP1 | OP0 | |||

| — | L | H | H | H | L | MA5 | MA4 | MA3 | MA2 | MA1 | MA0 | Mode register read (+CAS-2) | ||

| — | H | H | H | H | L | — | Reserved | |||||||

| R15 | R14 | R13 | R12 | L | H | R11 | R10 | R16 | BA2 | BA1 | BA0 | Activate-1 and -2 | ||

| R9 | R8 | R7 | R6 | H | H | R5 | R4 | R3 | R2 | R1 | R0 | |||

The CAS-2 command is used as the second half of all commands that perform a transfer across the data bus, and provides low-order column address bits:

- Read commands must begin on a column address which is a multiple of 4; there is no provision for communicating a non-zero C0 or C1 address bit to the memory.

- Write commands must begin on a column address which is a multiple of 16; C2 and C3 must be zero for a write command.

- Mode register read and some multi-purpose commands must also be followed by a CAS-2 command, however all the column bits must be zero (low).

The burst length can be configured to be 16, 32, or dynamically selectable by the BL bit of read and write operations.

One DMI (data mask/invert) signal is associated with each 8 data lines, and can be used to minimize the number of bits driven high during data transfers. When high, the other 8 bits are complemented by both transmitter and receiver. If a byte contains five or more 1 bits, the DMI signal can be driven high, along with three or fewer data lines. As signal lines are terminated low, this reduces power consumption.

(An alternative usage, where DMI is used to limit the number of data lines which toggle on each transfer to at most 4, minimises crosstalk. This may be used by the memory controller during writes, but is not supported by the memory devices.)

Data bus inversion can be separately enabled for reads and writes. For masked writes (which have a separate command code), the operation of the DMI signal depends on whether write inversion is enabled.

- If DBI on writes is disabled, a high level on DMI indicates that the corresponding data byte is to be ignored and not written

- If DBI on writes is enabled, a low level on DMI, combined with a data byte with 5 or more bits set, indicates a data byte to be ignored and not written.

LPDDR4 also includes a mechanism for "targeted row refresh" to avoid corruption due to "row hammer" on adjacent rows. A special sequence of three activate/precharge sequences specifies the row which was activated more often than a device-specified threshold (200,000 to 700,000 per refresh cycle). Internally, the device refreshes physically adjacent rows rather than the one specified in the activate command.[21][20]: 153–54

LPDDR4X

[edit]Samsung Semiconductor proposed an LPDDR4 variant that it called LPDDR4X.[22]: 11 LPDDR4X is identical to LPDDR4 except additional power is saved by reducing the I/O voltage (Vddq) from 1.1 V to 0.6 V. On 9 January 2017, SK Hynix announced 8 and 16 GB LPDDR4X packages.[23][24] JEDEC published the LPDDR4X standard on 8 March 2017.[25] Aside from the lower voltage, additional improvements include a single-channel die option for smaller applications, new MCP, PoP and IoT packages, and additional definition and timing improvements for the highest 4266 MT/s speed grade.

LPDDR5

[edit]On 19 February 2019, JEDEC published the JESD209-5, Standard for Low Power Double Data Rate 5 (LPDDR5).[26]

Samsung announced it had working prototype LPDDR5 chips in July 2018. LPDDR5 introduces the following changes:[27]

- Data transfer rate is increased to 6400 Mbit/s per pin

- Differential clocks are used (3200 MHz, DDR)

- Prefetch is not doubled again, but remains 16n

- The number of banks is increased to 16, divided into four DDR4-like bank groups

- Power-saving improvements:[26]

- Data-Copy and Write-X (all one or all zero) commands to decrease data transfer

- Dynamic frequency and voltage scaling

- A new clocking architecture, where commands use a quarter-speed master clock (CK), while data is transferred using full-speed Write Clock (WCK) & Read Strobe (RDQS) signals which are enabled only when necessary[26]

- One set of full-speed clocks per byte (vs. per 16 bits in LPDDR4)

- Elimination of the Clock Enable (CKE) pin; instead low-power mode is entered by a command over the CA bus, and lasts until the chip select signal next goes high

AMD Van Gogh, Intel Tiger Lake, Apple silicon (M1 Pro, M1 Max, M1 Ultra, M2 and A16 Bionic), Huawei Kirin 9000 and Snapdragon 888 memory controllers support LPDDR5.

The doubling of the transfer rate, and the quarter-speed master clock, results in a master clock which is half the frequency of a similar LPDDR4 clock. The command (CA) bus is widened to 7 bits, and commands are transferred at double data rate, so commands end up being sent at the same rate as LPDDR4.

| ↗ Rising clock ↗ | ↘ Falling clock ↘ | Operation | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| CA6 | CA5 | CA4 | CA3 | CA2 | CA1 | CA0 | CA6 | CA5 | CA4 | CA3 | CA2 | CA1 | CA0 | |||

| L | L | L | L | L | L | L | — | No operation | ||||||||

| H | L | L | L | L | L | L | — | Power-down entry | ||||||||

| L | H | L | L | L | L | L | — L — | Read FIFO | ||||||||

| H | H | L | L | L | L | L | — L — | Write FIFO | ||||||||

| L | L | H | L | L | L | L | — | Reserved | ||||||||

| H | L | H | L | L | L | L | — L — | Read DQ Calibration | ||||||||

| OP7 | H | H | L | L | L | L | OP6 | OP5 | OP4 | OP3 | OP2 | OP1 | OP0 | Multi-purpose command | ||

| OP7 | L | L | H | L | L | L | OP6 | OP5 | OP4 | OP3 | OP2 | OP1 | OP0 | Mode register write 2 | ||

| L | H | L | H | L | L | L | — | Self-refresh exit | ||||||||

| H | H | L | H | L | L | L | PD | DSE | — | Self-refresh entry | ||||||

| L | L | H | H | L | L | L | MA6 | MA5 | MA4 | MA3 | MA2 | MA1 | MA0 | Mode register read | ||

| H | L | H | H | L | L | L | MA6 | MA5 | MA4 | MA3 | MA2 | MA1 | MA0 | Mode register write 1 | ||

| L | H | H | H | L | L | L | AB | SB1 | SB0 | RFM | BG0 | BA1 | BA0 | Refresh | ||

| H | H | H | H | L | L | L | AB | — | BG1 | BG0 | BA1 | BA0 | Precharge | |||

| C5 | C4 | C3 | L | H | L | L | AP | C2 | C1 | BG1 | BG0 | BA1 | BA0 | Write 32 | ||

| WS_ FS |

WS_ RD |

WS_ WR |

H | H | L | L | WXSB /B3 |

WXSA | WRX | DC3 | DC2 | DC1 | DC0 | Column address select | ||

| C5 | C4 | C3 | C0 | L | H | L | AP | C2 | C1 | BG1 | BG0 | BA1 | BA0 | Masked Write | ||

| C5 | C4 | C3 | C0 | H | H | L | AP | C2 | C1 | BG1 | BG0 | BA1 | BA0 | Write | ||

| C5 | C4 | C3 | C0 | L | L | H | AP | C2 | C1 | BG1 | BG0 | BA1 | BA0 | Read | ||

| C5 | C4 | C3 | C0 | H | L | H | AP | C2 | C1 | BG1 | BG0 | BA1 | BA0 | Read 32 | ||

| R10 | R9 | R8 | R7 | L | H | H | R6 | R5 | R4 | R3 | R2 | R1 | R0 | Activate 2 | ||

| R17 | R16 | R15 | R14 | H | H | H | R13 | R12 | R11 | BG1 | BG0 | BA1 | BA0 | Activate 1 | ||

|

|

Compared to earlier standards, the nomenclature for column addresses has changed. Both LPDDR4 and LPDDR5 allow up to 10 bits of column address, but the names are different. LPDDR4's C0–C9 are renamed B0–B3 and C0–C5. As with LPDDR4, writes must start at a multiple-of-16 address with B0–B3 zero, but reads may request a burst be transferred in a different order by specifying a non-zero value for B3.

As with LPDDR4, to read some data requires 4 commands: two activate commands to select a row, then a CAS and a read command to select a column. Unlike LPDDR4, the CAS command comes before the read or write command. In fact, it is something of a misnomer, in that it does not select a column at all. Instead, its primary function is to prepare the DRAM to synchronize with the imminent start of the high-speed WCK clock. The WS_FS, WS_RD and WS_WR bits select various timings, with the _RD and _WR options optimized for an immediately following read or write command, while the _FS option starts the clock immediately, and may be followed by multiple reads or writes, accessing multiple banks.

CAS also specifies the "write X" option. If the WRX bit is set, writes do not transfer data, but rather fill the burst with all-zeros or all-ones, under the control of the WXS (write-X select) bit. This takes the same amount of time, but saves energy.

In addition to the usual bursts of 16, there are commands for performing double-length bursts of 32. Reads (but not writes) may specify a starting position within the 32-word aligned burst using the C0 and B3 bits.

LPDDR5X

[edit]On 28 July 2021, JEDEC published the JESD209-5B, Standard for Low Power Double Data Rate 5/5X (LPDDR5/5X)[30] with the following changes:

- Speed extension up to 8533 Mbit/s

- Signal integrity improvements with tx/rx equalization

- Reliability improvements via the new Adaptive Refresh Management feature

On 9 November 2021, Samsung announced that the company has developed the industry's first LPDDR5X DRAM. Samsung's implementation involves 16-gigabit (2 GB) dies, on a 14 nm process node, with modules with up to 32 dies (64 GB) in a single package. According to the company, the new modules would use 20% less power than LPDDR5.[31] According to Andrei Frumusanu of AnandTech, LPDDR5X in SoCs and other products was expected for the 2023 generation of devices.[32]

On 19 November 2021, Micron announced that Mediatek has validated its LPDDR5X DRAM for Mediatek's Dimensity 9000 5G SoC.[33]

On 25 January 2023 SK Hynix announced "Low Power Double Data Rate 5 Turbo" (LPDDR5T) chips with a bandwidth of 9.6 Gbps.[34] It operates in the ultra-low voltage range of 1.01–1.12 V set by JEDEC. It has been incorporated into the LPDDR5X standard as LPDDR5X-9600 making "LPDDR5T" a brand name.[35]

MediaTek Dimensity 9300 and Qualcomm Snapdragon 8 Gen 3 supports LPDDR5T.

On 17 April 2024 Samsung Electronics announced LPDDR5X-10700 with 25% higher bandwidth, 30% higher capacity and 25% improved power efficiency than previous LPDDR5X generations. This is achieved through a new 12 nm process that allows the chips to be more efficient while also being small enough to fit capacities of up to 32 GB in a single package.[36]

On 16 July 2024 Samsung has completed validation of the industry's fastest LPDDR5X DRAM, capable of operating at speeds up to 10.7Gbps, for use in MediaTek's upcoming flagship Dimensity 9400 SoC.[1]

LPDDR6

[edit]- Speed extension up to 14400 Mbit/s

- CAMM2

Notes

[edit]- ^ Equivalently, Mbit/s·pin.

References

[edit]- ^ a b "When is LPDDR3 not LPDDR3? When it's DDR3L..." Committed to Memory blog. Retrieved 16 July 2021.

- ^ "LPDDR". Texas Instruments wiki. Archived from the original on 5 March 2012. Retrieved 10 March 2015.

- ^ Anandtech Samsung Galaxy Tab - The AnandTech Review, 23 December 2010

- ^ a b JEDEC Standard: Low Power Double Data Rate 2 (LPDDR2) (PDF), JEDEC Solid State Technology Association, February 2010, retrieved 30 December 2010

- ^ "JEDEC Announces Publication of LPDDR2 Standard for Low Power Memory Devices". Press release. 2 April 2009. Retrieved 28 November 2021.

- ^ JEDEC publishes LPDDR3 standard for low-power memory chips Archived 20 May 2012 at the Wayback Machine, Solid State Technology magazine

- ^ a b JESD209-3 LPDDR3 Low Power Memory Device Standard, JEDEC Solid State Technology Association

- ^ "JEDEC Announces Publication of LPDDR3 Standard for Low Power Memory Devices". jedec.org. Retrieved 10 March 2015.

- ^ Want a quick and dirty overview of the new JEDEC LPDDR3 spec? EETimes serves it up Archived 2013-07-28 at the Wayback Machine, Denali Memory Report

- ^ Inside the Samsung Galaxy S4 Archived 2013-04-29 at the Wayback Machine, Chipworks

- ^ Samsung LPDDR3 High-Performance Memory Enables Amazing Mobile Devices in 2013, 2014 - Bright Side of News

- ^ "Samsung Exynos". samsung.com. Retrieved 10 March 2015.

- ^ Samsung reveals eight-core mobile processor on EEtimes

- ^ Now Producing Four Gigabit LPDDR3 Mobile DRAM, Using 20nm-class* Process Technology, Businesswire

- ^ Snapdragon 800 Series and 600 Processors Unveiled , Qualcomm

- ^ "JEDEC to Focus on Mobile Technology in Upcoming Conference". jedec.org. Retrieved 10 March 2015.

- ^ "Samsung Develops Industry's First 8Gb LPDDR4 Mobile DRAM". Samsung Tomorrow (Official Blog). Samsung Electronics. Archived from the original on 1 October 2014. Retrieved 10 March 2015.

- ^ http://www.softnology.biz/pdf/JESD79-4_DDR4_SDRAM.pdf JESD79 DDR4 SDRAM Standard

- ^ 'JEDEC Releases LPDDR4 Standard for Low Power Memory Devices', JEDEC Solid State Technology Association.

- ^ a b c JEDEC Standard: Low Power Double Data Rate 4 (LPDDR4) (PDF), JEDEC Solid State Technology Association, August 2014, retrieved 25 December 2014 Username and password "cypherpunks" will allow download.

- ^ "Row hammer refresh command". Patents. US20140059287. Retrieved 10 March 2015.

- ^ Reza, Ashiq (16 September 2016). "Memory Need" Gives Birth To "New Memory" (PDF). Qualcomm 3G LTE Summit. Hong Kong.

- ^ Shilov, Anton. "SK Hynix Announces 8 GB LPDDR4X-4266 DRAM Packages". Retrieved 28 July 2017.

- ^ "SK하이닉스 세계 최대 용량의 초저전력 모바일 D램 출시". Skhynix (in Korean). Archived from the original on 13 January 2019. Retrieved 28 July 2017.

- ^ "JEDEC Updates Standards for Low Power Memory Devices". JEDEC. Retrieved 28 July 2017.

- ^ a b c "JEDEC Updates Standard for Low Power Memory Devices: LPDDR5". jedec.org. Retrieved 19 February 2019.

- ^ Smith, Ryan (16 July 2018). "Samsung Announces First LPDDR5 DRAM Chip, Targets 6.4Gbps Data Rates & 30% Reduced Power". AnandTech.

- ^ "LPDDR5/5X 协议解读(三)WCK operation", Zhihu (in Chinese and English), 19 December 2022, retrieved 4 November 2023

- ^ Chang, Alex (Yeongkee) (October 2019), "Commands & New Features" (PDF), LPDDR5 Workshop, retrieved 4 November 2023

- ^ "JEDEC Publishes New and Updated Standards for Low Power Memory Devices Used in 5G and AI Applications". jedec.org. Retrieved 28 July 2021.

- ^ "Samsung Develops Industry's First LPDDR5X DRAM". Samsung.com. 9 November 2021. Retrieved 9 November 2021.

- ^ Frumusanu, Andrei (9 November 2021). "Samsung Announces First LPDDR5X at 8.5Gbps". Anandtech.com. Retrieved 9 November 2021.

- ^ "Micron and MediaTek First to Validate LPDDR5X". Micron Technology.

- ^ "SK hynix Develops World's Fastest Mobile DRAM LPDDR5T". 24 January 2023. Retrieved 12 June 2023.

- ^ Hung, Vuong. "Jedec Memory for Automotive LPDDRx & UFS" (PDF). jedec.org. p. 4. Retrieved 18 April 2024.

- ^ "Samsung Develops Industry's Fastest 10.7Gbps LPDDR5X DRAM, Optimized for AI Applications". Samsung Newsroom. 17 April 2024. Retrieved 18 April 2024.

External links

[edit]- JEDEC pages: LOW POWER DOUBLE DATA RATE 3 SDRAM (LPDDR3)